����DSP��Զ�̳�����·����ܶ�[12]��������д��ʱ���Ҫ��ϵͳ���ܶϵ磬�����������ϵͳ����������ֻ���˹�ͨ��JTAG�ڵ�����д���ָܻ��������Ч���ϵͳά���Ŀɿ��Գ�Ϊһ����Ҫ�����⡣���Ĵ��µ�������ڶ�DSP�ij����Ƭ�����ݷֶεĸ߿ɿ���Զ�̸���������ƣ����о��˶����ǿ�ɿ��Ե�Ӧ�÷�����������ij�ͺ�����Զ�̼��ϵͳΪ����������������Ƶ�ʵ��Ӧ�á�

1��ϵͳ�ṹ

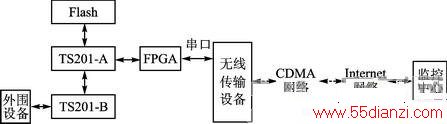

��ϵͳ�������ݶ࣬�����������к�ǿ��ʵʱ��Ҫ��ѡ��ADI��˾�ĸ��ٴ���оƬTigerSharc201s��Flashѡ��JS28F128������Ϊ256 Mb��ϵͳ��Ʋ�����ƬADSP���е�ģʽ��ϵͳ�ṹ��ͼ1��ʾ��TS201AΪ��DSP��TS201BΪ��DSP����DSP��Flash����EPROM���ط�ʽ����ͨ��Link���������ش�DSP��������ϵͳ֧�ֶ��ֹ���ģʽ���������ͨ���ڲ�Э��Զ�̹ܿش���ϵͳ����DSPʵ���źŴ������㣬�Ѵ������������ݸ���DSP;��DSPʵ�ֹܿ�ģ�飬ͨ����ΧоƬFPGA�Ĵ���Э�鷢�����ߴ����豸��ͨ��CDMAģ���������������ʽ�����͵���������������������ͨ��Э������ʵ��Զ�̹������������ݿ��ļ����¡�������º�״̬ģʽת����

ͼ1��ϵͳ�ṹ

2��Զ�̸���ԭ����ʵ��

2.1�����ԭ��

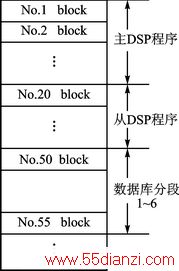

Flash�ڲ���Ϊ256��bLOCk�����Բ�д����λ�õ�block�Σ�û�в�д��block���ݲ��ᶪʧ��������һ���ԣ�����ƬDSP��������ͷֶε����ݿ����дλ�÷ֿ���Flash�ռ��ַ������ͼ2��ʾ��

ͼ2��Flash�ռ��ַ����ʾ��ͼ

������İ����ڲ�Э������ݿ������ļ��ְ���ͨ�����������·�����TS201Ϊ���ĵ��źŴ����������������������ݺ�ͨ����������д���ܣ����������Զ�д��Flash�С�����������DSP����ʵ��Զ�̷�Ƭ���³���Ĺ��ܡ�����ij�ʼ�������У�ÿ�λ��Զ�����Flash�е����ݣ���ɸ������ݿ�����Ĺ��ܡ�

Ϊ������Զ�̸��µĿɿ��ԣ�����ƬDSP����ֿ�λ����д��������DSPֻ�漰�������ƹ��ܣ�������DSP������Ϊ����ϵͳ��“��”��һ�㲻�����¡��ô�DSPʵ������Ҫ�����ܼ��㣬���ļ���ͨ����DSP��Link���������������ֵ�����ά�����㷨��������ͨ�����´�DSP������ɡ��ڸ��µĹ����У���DSP������Ӱ�죬��ǿ��ϵͳ�Ŀɿ��ԣ�Ҳ���ص���ͻȻ����ᵼ��ϵͳ�����ı�����

2.2������TS201��Զ�̸��¹���

��ϵͳ�ƶ��ڲ�Э�飬ʵ��Զ�̸��µ�ָ������źŴ���������ָ�����Э�����Զ�̸��µ����ݣ���Ϊ�������»������ݿ���¡���Ϊ��������������������DSP��������;��Ϊ���ݿ���£��������ݿ���Ϣ�������µ�λ�úͶ�����

��ϵͳ�����ݿ��ļ�Ϊ30K×4�ֽڣ���Ϊ6�Ρ��������ߴ����豸�ķ��������������ݰ���ÿ��198�ֽڷְ���ÿ��������ͷ���ܰ��������ź�У��λ����Ϣ������Э������ʽ���£�![]()

��ͷ��SOH;

���ij��ȣ��������ݵij��ȣ�������ͷ���̶�Ϊ198;

�ܰ������˴γ���������ݿ��ļ��ֳɵ��ܰ���;

���ţ������ı��;

���ݣ���Ҫ���µ�����;

У��λ��ռ3���ֽڣ�����1���ֽڵ���żУ��λ��2���ֽڵ�CRCУ��λ��

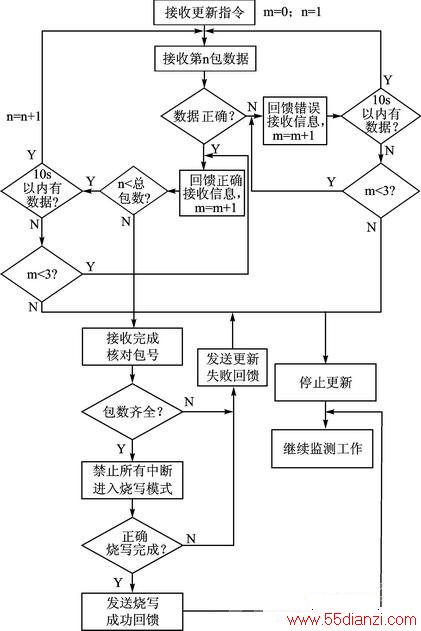

�������ļ�ʱ��ϵͳ��������Э�顣�źŴ�����ÿ���յ�1�����ݣ�����������Ϣ��������ģ�������Ľ��յ��ɹ�������Ϣ���ٷ���1�����ݡ�������ȴ�ģʽ��10 s���Զ��ط��˰����ݡ��������ط�3����Ȼ���ɹ����ŷ����˴θ��¡��źŴ������������ƺͼ������һ�������ͻ��������ȴ�ģʽ��10 s���Զ����·��ͻ�����Ϣ������ط�3�Σ��ŷ������£����»ص�����״̬��ֱ�����յ��µ��·�ָ�

�źŴ�����������ȫ�������ݰ���Ҫ���а��ź˶ԣ�ȷ���������Э��֪ͨ������ļ���������дģʽ������Flash�ض��Ķ�дָ���RAM�е�������Flash�ĵ�20��block��ʼλ�ÿ�ʼд�롣��������ݿ⣬����Э�������ݶκţ�����д��ʼλ�ø�Ϊ��Ӧblock�ĵ�ַ����д��ɺ���д�ɹ�������Ϣ������������ġ��ڲ��ϵ������£�ϵͳ��ʱ��Ȼ�ǰ��վɵ������汾���С�ϵͳ�����Զ�̵�Ӳ������ͨ��ָ����Ƽ̵������̵������ӵ�Դģ�飬ʵ�ֶ��ݵĶϵ繦�ܣ��Ӷ�ʵ��DSP�����¼��أ���ɳ���������ݿ���¡���ϸ��Զ�̸���������ͼ3��ʾ��

ͼ3��Զ�̸�������

2.2.1��FPGA����ʵ��

FPGA����Ƭѡ�����źţ�TS201Ϊ�����豸��Ϊ�˲�Ƶ�����TS201�Ľ��̣���FPGA�����9���ֽڵ�FIFO��FIFO������TS201����IRQ�ⲿ�ж��źţ�֪ͨTS201��ȡ���ݣ�FPGA����1�����ź����FIFO�е�1�����ݡ�

2.2.2��TS201�жϳ���ʵ��

���ڲ����жϵķ�ʽ���գ������ISR����ʵ�����£�

interrupt(SIGIRQ1, isr_UART2);//���ô����жϵ�ַ

interrupt(SIGTIMER1LP,TIMER1_ISR); //���ö�ʱ���жϵ�ַ

void isr_uart2() {

int i;

int buf_uart[9];

for(i=0;i<9;i++){

buf_uart[i]=*UART_ADD_2;//��ȡ�������ϵ�����

buf_uart[i] =buf_uart[i] & 0xff; //���������ߴ��ţ�ֻȡ�������ϵĵ�8λ

}

……

}

�� ��ʱ��������ơ�TS201��Timer0��Timer1������ʱ����ÿ����ʱ���ַ�Ϊ��λ�͵�λ�����Ĵ�������ϵͳ����Timer1�ĵ�λ�Ĵ�����10 s��ʱ��

void TIMER1_ISR( ){

int i,tempp;//�رն�ʱ��

tempp=__builtin_sysreg_read(__INTCTL);

tempp=tempp & (0xFFFFFFFF ^INTCTL_TMR1RN);

__builtin_sysreg_write(__INTCTL, tempp);

NumberTimer++;

if(NumberTimer==3) { //����Ѿ��ط�3��

Variable_Init( );//��ʼ������

}

else{

SendCopyData( ); //�ط�֮ǰ����Ϣ

__builtin_sysreg_write(__TMRIN1H, 0x0); //��λ�ij�ʼ���DZ����

__builtin_sysreg_write(__TMRIN1L, CK10); //����Timer1��λ�Ĵ���������ʱ10 s���¿�����ʱ��

tempp=__builtin_sysreg_read(__INTCTL);

tempp=tempp | INTCTL_TMR1RN;

__builtin_sysreg_write(__INTCTL, tempp);

}

}

���У���ʱ���ļ���������CCLK/2�����ԣ�CK10=CCLK/2×10;

2.2.3��Flash����ʵ��

TS201�����ⲿ�豸Flash�Ķ�д����ֻ��ͨ��DMA���У���ϵͳ��Ʋ���DMA0������Ĵ������£�

void dma0_ISR( ){

return;

}

void WriteFlash( int Offset, int nValue ){//��Flash��Offsetλ��д��nValue

int temp=nValue;

TCB_temp.DI=&temp;

TCB_temp.DX=0x00010001;

TCB_temp.DY=0;

TCB_temp.DP=0x43000000;

q=__builtin_compose_128((long long)TCB_temp.DI | (long long)TCB_temp.DX����32, (long long)(TCB_temp.DY | (long long)TCB_temp.DP����32));

__builtin_sysreg_write4(__DCS0, q);

TCB_temp.DI=(int*)(Offset);

TCB_temp.DX=0x00010001;

TCB_temp.DY=0;

TCB_temp.DP=0xc3000000;

q=__builtin_compose_128((long long)TCB_temp.DI | (long long)TCB_temp.DX����32, (long long)(TCB_temp.DY | (long long)TCB_temp.DP����32));

__builtin_sysreg_write4(__DCD0, q);

���Ĺؼ��֣����� �ɿ��� ������� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����