ELSIF s[5..4]= =2 THEN

d=(li[11..0]>H”80“);

ELSIF s[5..4]==3 THEN

d=(1i[11..0]>H”100”);

END IF;

IF fq3= =O THEN

lO[11..O]=O;

ELSE lo[11..O]=li[11..O];

END IF;

END;

在无语音目噪声低于门限值时,mx_t的输出信号d为0,经触发器DFF对信号整形后输出0到后延时计数器清零端,计数器脱离清零状态,对时钟bclk计数。计数到第8个脉冲时,bq3变高,经反相后封住计数器,停止计数,保持bq3为高。同时bq3的高电平对前延时计数器清零,使其输出信号fq3为0。mx_t根据fq3的值使输出信号li[11..0]为0,噪声不能输出。

当短促噪声到来时,瞬时超过噪声门限值,使d瞬时为高,后延时计数器清零,bq3变低,前延时计数器脱离清零状态开始计数。但未及计数到硒3为高,噪声已回落到门限以下,D触发器的输出经反相后变高,经过与门、或门对前延时计数器清零,使fq3维持为0,噪声仍不会输出。只有当输入超过门限值一定的时间,足以使计数器计到fq3为高时,mx_t才使输入信号原样输出。

在fq3变高后,如因语音短暂变弱或停顿,mx_t的输出d转为0,后延时计数器脱离清零状态开始计数。但只要语音在一定的时间里重新转强,后延时计数器就再次被清零,bq3维持为0,fq3维持为高,语音输出就始终不会间断。

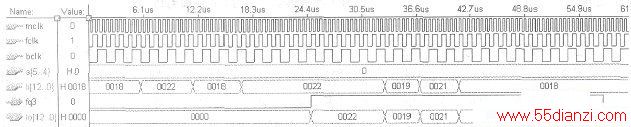

在MAX+plusⅡ软件里,对上图电路仿真的结果如图5所示。为使波形直观,仿真时对输入信号li[12..]0的周期做了压缩。语音信号的真实变化比图示要缓慢得多。

当s[5..4]取值0时,静噪门限值是20。从上图可见,-开始li[12..0]输入值小于20时,输出10[12..]是0,即使有大于20的值短暂出现,输出也为0。只有当大于20的信号持续一定时间(前延时)后,fq3变高,输出lo[12..0]才变得和输入li[12..0]一样。此后如输入信号短暂低于20,输出仍和输入一样。只有当输入小信号保持一定时间(后延时)后,fq3才变低语音被关断。

本文关键字:语音 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:基于FPGA技术实现DDS的方案