本文将为大家介绍一类重要的可编程逻辑器件——FPGA,并应用FPGA来实现一些较复杂的数字语音处理功能,如语音音量调节、语音静态噪声控制等。

一,FOGA与OLD的异同

FPGA(现场可编程门阵列)也是一种可编程逻辑器件,在原理及应用上与PLD器件并没有本质的区别。事实上,在可编程逻辑器件发展的早期,这两个名称在使用上是不太严格的,如ALTEra公司的早期技术文件中就把FLEX系列和ACEX系列的器件称为“CPLD(复杂可编程逻辑器件)”,而现在则把它们归为。FPGA器件。一般来讲,在芯片的内部架构上,PLD采用的是“Product Term(乘积项)”技术,而FPGA则采用了“Look—Up Table(查找表)”技术。由于芯片架构的不同,大多数FPGA芯片内部除了逻辑单元外,还构建有一定容量的存储器单元,可被设计成各种类型的数据存储器使用。在对器件编程时,PLD内部使用EEPROM来存储编程数据,断电后数据不会消失;而FPGA内通常采用SRAM,数据在断电后就消失,因此必须用“Configuration(配置)”技术在上电时重新向FPGA注入编程数据,这使得FPGA在使用上略为复杂些。但由于FPGA具有逻辑资源丰富、成本低、功耗小等优势,其产量现已超过了PLD,成为可编程逻辑器件的主要类型。 Altera公司的MAX+plusⅡ软件同样支持FPGA芯片的应用。因此,无需多了解FPGA在内部架构上和PLD芯片的差异,也能够用MAX+pluSⅡ软件来设计FPGA。

二、FPGA的配置电路

使用FPGA时,除了要注意芯片的电源电压可能不同外,最主要的特点是需要为FPGA增加一个配置电路,这点在设计电路图和印制电路板时不可忽略。向FPGA配置数据的方法有好多种,常用的有JTAG接口配置电路、外部芯片配置电路等。在FPGA芯片的调试过程中,编程数据经常要修改,这时最方便的办法是用PC机通过下载电缆向FPGA芯片的JTAG接口下载配置数据。配置数据的文件是在项目编译的过程中自动生成的,其扩展名是.SOF,以区别于扩展名为.pof的编程数据文件。当在MAX+plusⅡ软件的Programmer界面里载入.sol文件时,界面中的Program选项呈现不可用的灰色,Configure则成为可用的选项。JTAG接口配置电路的缺点是断电后数据消失,再次上电后需要重新下载。因此当电路调试结束,需要把配置数据固化保存时,可以选用Altera公司的EPC等系列配置芯片,用类似于烧写单片机ROM的办法把MAX+plusⅡ里生成的.pof文件写入配置芯片。现在市面上大多数的编程器都支持烧写EPC系列配置芯片。把固化了数据的配置芯片通过配置电路接到FPGA,每次上电时FPGA从配置芯片处取得数据自动完成配置过程,所设计的逻辑功能就能在FPGA上实现了。

三、使用FPGA的数字语音实验电路

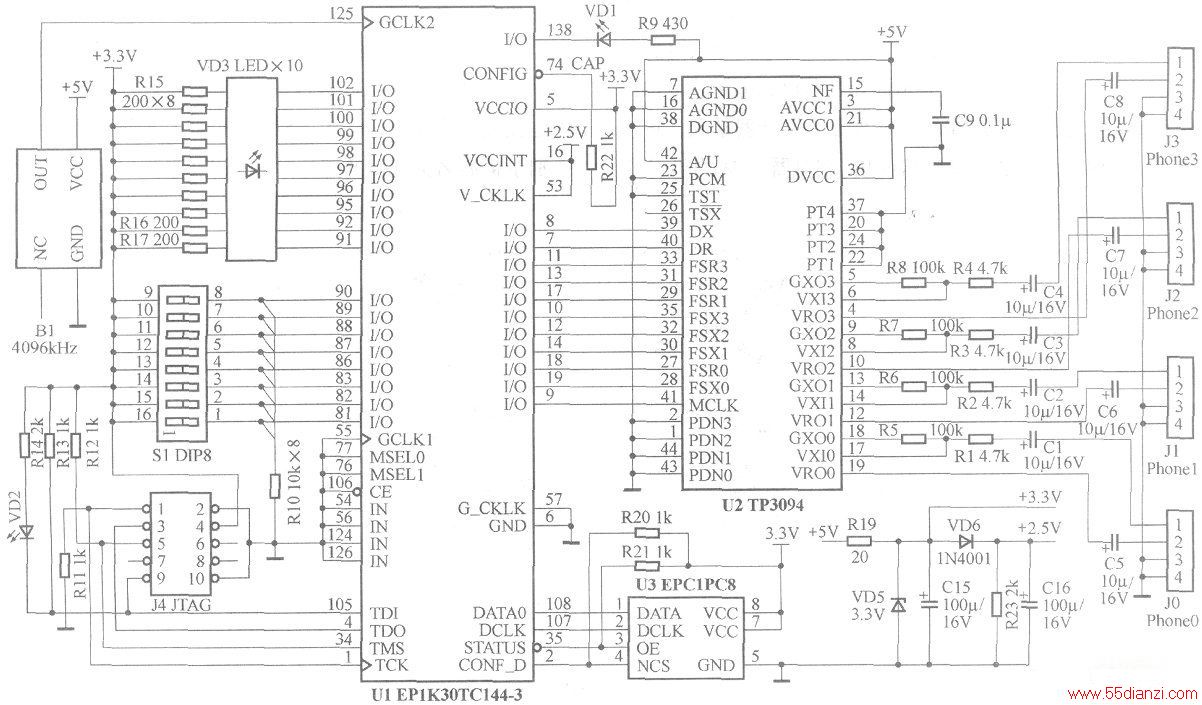

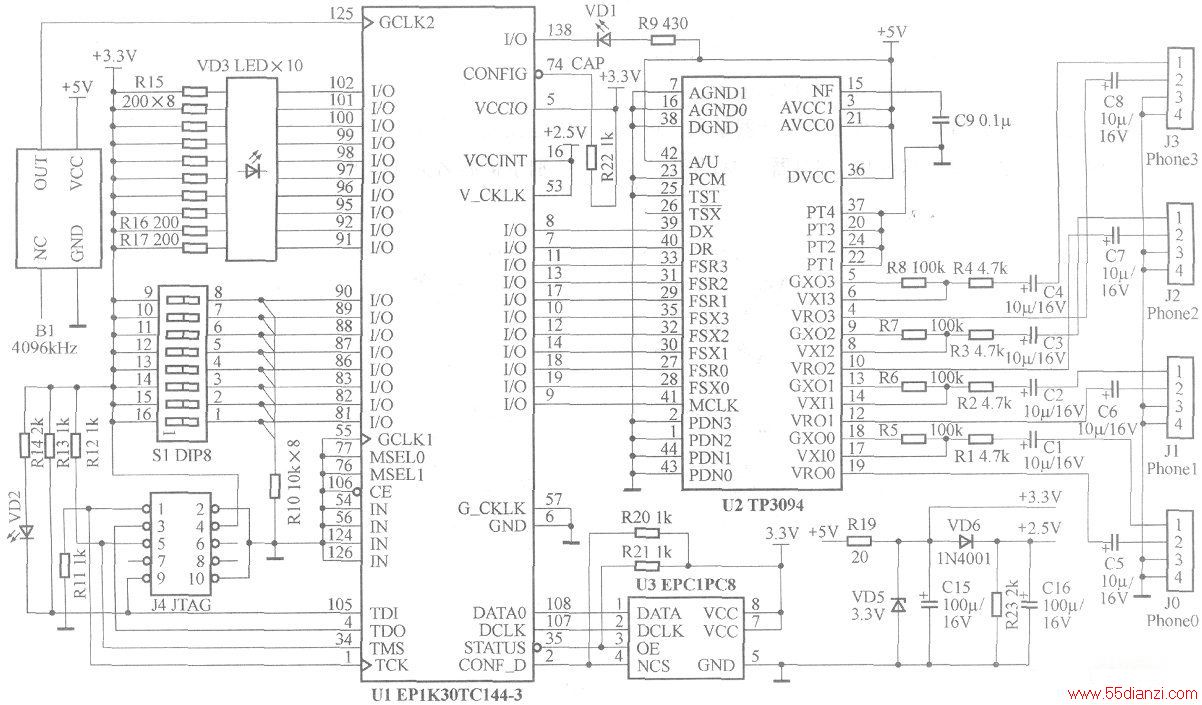

用FPGA芯片取代前几讲实验电路里的PLD芯片,再改变一下电源电路,增加配置电路,就可做成用FPGA来设计数字语音电路的新实验电路板,其电路图如下图所示。

图1中FPGA选用了Altera公司的ACEX1K系列芯片EP1K30TC144-3,其内部不仅有1728个逻辑单元,还有24576bit的片上存储器(RAM)可供设计使用。这个器件使用3.3V的I/0接口电压和2.5V的内核电压。为简化电源电路,图1中用了一个稳压二极管来得到3.3V的电压,再通过一个IN4001二极管的正向压降降低0.7V来取得近似2.5V的电压。图中配置芯片选用:EPCIPC8型,具有1Mbit的数据存储量。它与电阻R20、R21组成配置电路,连接到FPGA的各配置功能引脚,即U1的第2、35、107、108诸引脚。其余和配置有关的第76、77、106、74各引脚则分别接地或高电平。当用JTAG接口下载配置数据到FPGA时,不插EPCIPC8芯片。电路的其余部分除了一些电阻的参数有所调整外,和原来的实验板基本相同。

FPGA语音实验板电路完整的Protel设计文件,包括电原理图和印制电路板图。

四.语音音量调节电路

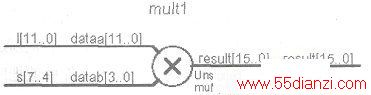

由于FPGA内具有更丰富的逻辑资源,我们可用它来做一些耗用较多逻辑单元的设计,比如把输入语音数据送到一个乘法器,和外部设置的数值做乘法运算,得到的乘积作为输出语音数据。改变设置的数值,输出语音的音量就随之改变,这样就实现了语音的放大和音量调节。 在MAX+pluSⅡ软件的功能插件管理器里,提供了参数化乘法器的图形设计向导。使用时只要选定乘法器的几个参数,如被乘数、乘数、乘积的数据宽度等,就能立即得到所需要的乘法器,如下图所示。

上图的上半部分基本上就是以前介绍过的电话广播电路,当S[3..0]设置为1010时,0号用户可向其余用户进行语音广播。不同的是,在这里从dx输入的语音信号不是直接送到dr,而是送到s2p模块进行串/并行转换,得到的8位并行数据d[7..0]由D触发器阵列DFFE锁存为A律码a[7..O]。图中DFFE的输入和输出都是8位总线,表示由8个D触发器组成的阵列,时钟mclk和装载信号load是公用的。用D触发器做锁存器的优点是锁存操作由输入时钟信号的上升沿完成,在时间上比电平控制型的锁存器更精确。锁存后的A律码通过a2_t模块转换为线性码,经过静噪电路jz完成静噪控制,经12a_t模块转换回A律码,再通过p2s模块转换为串行语音数据,从dr输出。mxzsd信号用于门限指示,当静噪门限被打开时点亮门限指示灯。

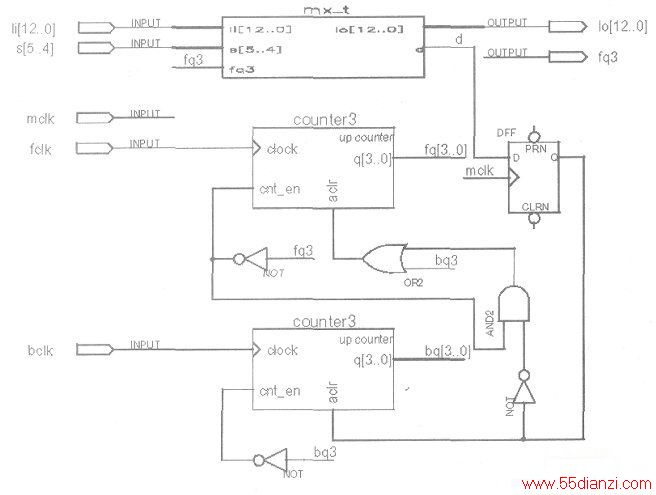

上图中除jz以外的电路符号以前都介绍过,这里只对静噪电路jz作说明。在MAX+plusⅡ软件中,双击打开它,电路如图4所示。下图里,上、下两个counlter3计数器各对前延时时钟fclk和后延时时钟bclk计数,起到前、后延时的计时作用。mx』是静噪门限判别电路的符号,由AHDL文本文件转换而来,可根据拨动开关设置的数值s[5..4]判别输入的语音1[12..O]是否超过了噪声门限,如超过则输出d为高电平。

上图的上半部分基本上就是以前介绍过的电话广播电路,当S[3..0]设置为1010时,0号用户可向其余用户进行语音广播。不同的是,在这里从dx输入的语音信号不是直接送到dr,而是送到s2p模块进行串/并行转换,得到的8位并行数据d[7..0]由D触发器阵列DFFE锁存为A律码a[7..O]。图中DFFE的输入和输出都是8位总线,表示由8个D触发器组成的阵列,时钟mclk和装载信号load是公用的。用D触发器做锁存器的优点是锁存操作由输入时钟信号的上升沿完成,在时间上比电平控制型的锁存器更精确。锁存后的A律码通过a2_t模块转换为线性码,经过静噪电路jz完成静噪控制,经12a_t模块转换回A律码,再通过p2s模块转换为串行语音数据,从dr输出。mxzsd信号用于门限指示,当静噪门限被打开时点亮门限指示灯。

上图中除jz以外的电路符号以前都介绍过,这里只对静噪电路jz作说明。在MAX+plusⅡ软件中,双击打开它,电路如图4所示。下图里,上、下两个counlter3计数器各对前延时时钟fclk和后延时时钟bclk计数,起到前、后延时的计时作用。mx』是静噪门限判别电路的符号,由AHDL文本文件转换而来,可根据拨动开关设置的数值s[5..4]判别输入的语音1[12..O]是否超过了噪声门限,如超过则输出d为高电平。

mx_t还根据输入的fq3信号来完成静噪控制功能,当fq3为0时使输出lo[11..0]为0(静音),当fq3为1时则使输出lo[11..0]等于输入的语音li[11..0]。语音的符号位不变,始终是Io12=li12。mx_t的程序如下:

UBDESIGN mx_t

(li[12..0],s[5..4],fq3:INPUT;

lo[12..0],d:OUTPUT)

BEGIN

lo12=li12;

IF s[5…4]==O THEN

d=(li[11..0]>H“20”);

ELSIF s[5..4]==1 THEN

d=(li[11..0]>H”40”);

本文关键字:语音 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:基于FPGA技术实现DDS的方案