1.前 言

随着集成电路复杂度越来越高,测试开销在电路和系统总开销中所占的比例不断上升,测试方法的研究显得非常突出。目前在测试源的划分上可以采用内建自测试或片外测试。内建自测试把测试源和被测电路都集成在芯片的内部,对于目前SOC级的芯片测试如果采用内建自测试则付出的硬件面积开销则是很大的,同时也增加了芯片设计的难度:因此片外测试便成为目前被普遍看好的方法。由于FPGA具有可重构的灵活性,利用FPGA来作为测试源实现片外测试就是一种非常有效的手段。

由于伪随机模式测试只需要有限个数的输入向量便可达到很高的故障覆盖率因而在作为测试源设计中得到了广泛应用,采用CPLD来实现伪随机测试序列生成器的设计[1]为提供了电子系统测试信号提供了一种简单的方法。在可测试设计中同时也要考虑低功耗的问题,考虑功耗的主要原因是在测试模式下电路的功耗要远远高于正常模式。因为采用完全的单输入跳变测试序列所需要的测试序列长度太长而没有实际应用价值,这样获得准单输入跳变测试序列的测试生成器一直是低功耗设计中一种非常有效的方法,本文针对一种产生准单输入跳变测试序列的低功耗测试生成器[2]的缺点提出了改进设计方案,并且利用EDA技术在FPGA芯片上进行了设计实现。

2.低功耗测试生成器的设计

本文给出的低功耗测试产生器改进方案是在文献[2]的测试产生器的基础上再利用ROM中的种子对LFSR的再播种实现的。因为原有低功耗测试产生器是以LFSR为基础的,其产生的准单输入跳变测试序列只能覆盖被测电路中的易测故障;要达到1 0 0%的故障覆盖率,就必须对被测电路中剩余的抗伪随机故障和难测故障采用少量的确定模式测试集来覆盖;折叠集[3]就是其中一种有效的确定模式测试集,利用存储在ROM中的折叠种子对LFSR多次再播种就可以产生所需要的折叠测试序列。由于在折叠集内部各个测试向量之间由于存在相关性,按照一定规律排序后就可以将南一个折叠种子产生的折叠集变换成单输入跳变测试序列:这样由不同的折叠种子产生的测试向量序列就是准单输入跳变测试序列。

设LFSR的级数为n,开始由LFSR产生一定长度的准单输入跳变测试序列,具体产生原理和改进前的低功耗测试产生器[2]原理一样;然后开始由折叠控制器装入一个折叠种子,然后产生单输入跳变测试序列,折叠控制器由图1中的计数器与解码器组成,解码器完成对由一一个折叠种子产:生的原始折叠集的排序产生单输入跳变测试序列。然后再装入下一个折叠种子,折叠控制器接着产生下一个单输入跳变测试序列,这样直到所有的折叠种子都被装入为止。整个的由不同的折叠种子产生的测试向量序列就是准单输入跳变测试序列。

3.FPGA的设计实现

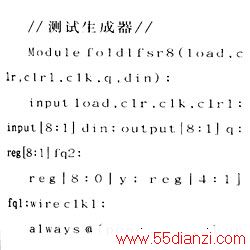

在FPGA的设计输入时采用Verilog HDL语言来设汁所要求的测试生成器模块,我们以n=8的LFSR为例,以下给出了设计源码。通过使用MaxplusII1 0.2软件在ALTERA公司的FPGA芯片FLEX EPF1OK 10LC84-4进行了仿真,图2给出了仿真波形,验证了设计的正确性。

本文关键字:生成器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术