四相相移键控调制(Quaternary Phase Shift Keying,QPSK)是一种线性窄带数字调制技术,它已经在数字调制技术中占有重要的地位,被广泛地应用于卫星通信、移动通信、视频会议系统、蜂窝电话和其它数字通信领域。具有频带利用率高、频谱特性好、抗衰落性能强、较低的比特错误率等优点。

DSP 技术主要是指将DSP的基本理论和算法付诸实现的途径和方法。传统的DSP技术是当前广泛使用的DSP 处理器 的 解决方案 ,而这种解决方案日益面临着不断增加的巨大挑战,自身的技术瓶颈导致这种解决方案在DSP许多新的应用领域中的道路越走越窄。而现代DSP技术是相对于传统DSP技术而言的,是基于可编程片上系统SOPC( System ON a Programmable Chip)技术、 EDA 技术与 FPGA 实现方式的DSP技术,是现代 电子 技术发展的产物,它有效地克服了传统DSP技术中的许多瓶颈,在许多方面显示了突出的优势,如高速与实时性,高可靠性,自主知识产权化,系统的重配置与硬件可重构性,单片DSP系统的可实现性以及开发技术的标准化和高效率。QPSK设计采用MATLAB/Simulink DSP Builder开发出用于QPSK调制的正交信号产生单元,在 电路 模块的形成方式上用DSP Builder的模块调用代替繁琐的VHDL程序,从而方便的得到了所需的结果。系统的实现以FPGA为物理载体,与传统的基于硬件描述语言的设计相比,这种流程更快捷方便灵活。

1 QPSK调制原理

所谓的QPSK调制就是利用载波的四种不同相位来表征数字信息,每一种载波相位代表两个二进制代码元信息。由于每一个载波相位代表两个二进制码元信息,所以每四个二进制码元又被称为双比*元。

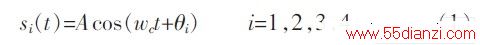

QPSK信号的表示式为

其中,A为载波振幅,wc为载波角频率,θi为载波相位。

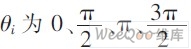

若 ,则QPSK信号的初始相位为0,若

,则QPSK信号的初始相位为0,若 ,则QPSK信号的初始相位为π/4。

,则QPSK信号的初始相位为π/4。

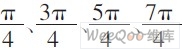

将式(1)写成

I(t),Q(t)为+1或-1。则式(3)即为QPSK的数学表达式。

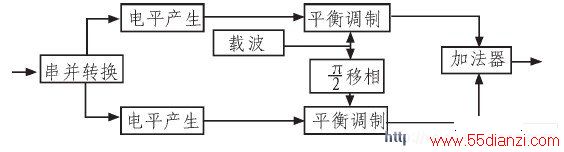

QPSK信号的调制可分为相位选择法和调相法,本文采用调相法进行设计,其调制框图如下图1所示。

图1 QPSK调相法调制框图

图1中,串/并 变换器 将输入的二进制序列依次分为两个并行的双极性码序列。设二进制数分别为a和b。双极性的a和b脉冲通过两个平衡 调制器 分别对同相载波和正交载波进行二相调制,两路输出叠加后就可以得到QPSK信号。

2 基于DSP Buildter的QPSK设计

DSP Builder可完成图形化的系统建模、设计、仿真、把设计软件下载到FPGA 开发板 上。它是一个系统级的 开发工具 ,架构在多个软件之上,并把系统级和RTL级两个设计领域的设计 工具 连接起来,最大程度的发挥了两种工具的优势。DSP Builder依赖MathWorks公司的数学分析工具Matlab/Simulink,以Simulink的BLOCkset出现,可以在Simulink中进行图形化设计和仿真,同时通过SignalCompiler可以把Matlab /Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。而对后者的处理可以由FPGA/CPLD开发工具QUARTusⅡ来完成。

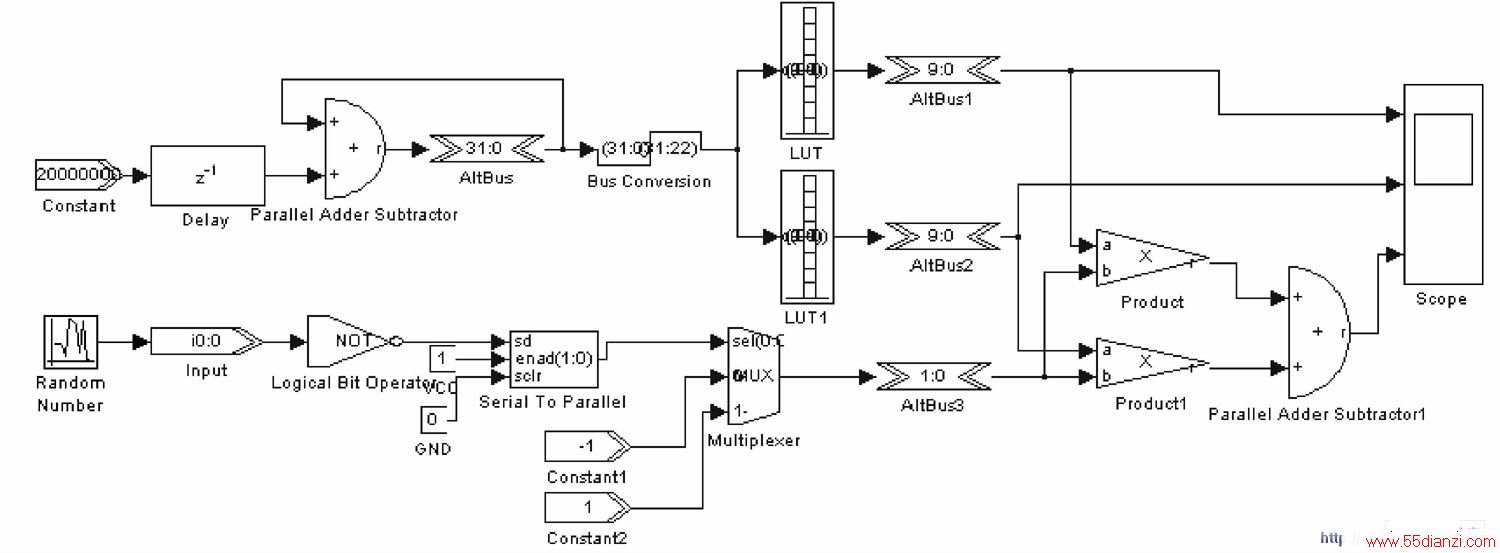

研究采用QuartusII6.1、DSP Builder6.1和Madab Rb2006作为FPGA的设计及测试平台。因此,在设计的过程中可以很方便的调用DSP-Bbuilder和Simulink库中的图形模块来建立硬件模型,输入信号也可方便的调用Simulink模块。依据QPSK的基本原理,可以快速的建立QPSK模型。要完成QPSK的建模,首先打开MATLAB,在命令窗口输入“Simulink”进入图形化仿真建模环境,新建一个仿真模型。依照图1的原理图设计,建立模型如图2所示。

图2 QPSK调制系统的整体模型

图2中,由频率字、延时器、加法器和两个LUT组成正交 信号发生器 ,产生两个正交的载波信号。随机信号发生模块产生随机信号,经过反相器形成数字基带信号,经过串并 转换模块 变为并行信号,再经过多路选择器模块输出+1和-1,然后和正交信号 发生器 产生的正交载波信号相乘,最后在加法器中进行相加实现QPSK调制。

3 系统仿真与硬件测试

3.1 系统仿真

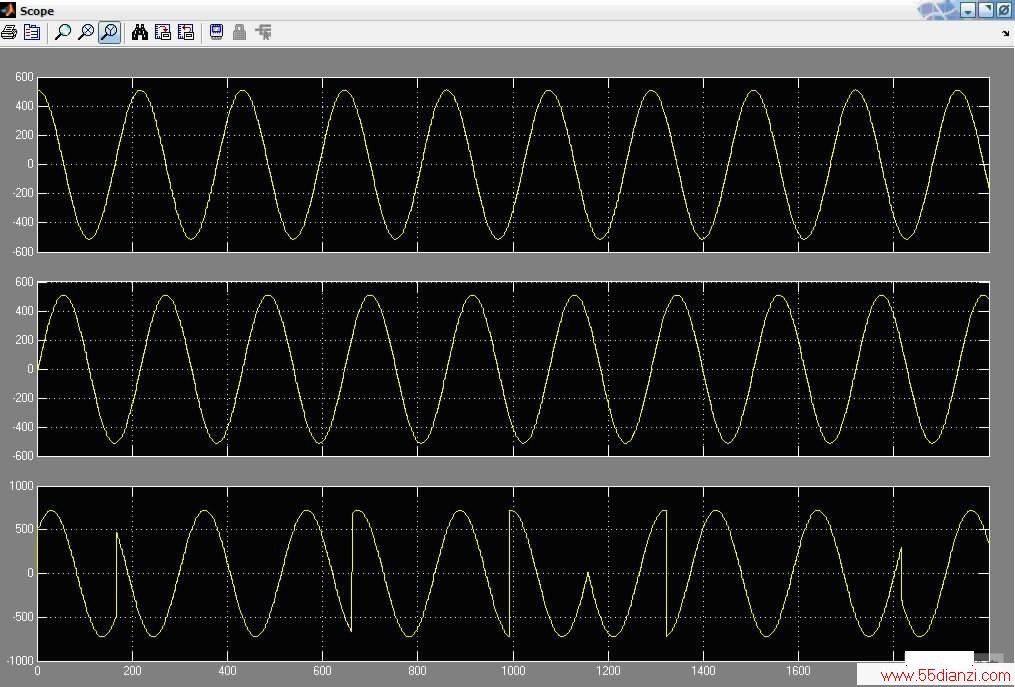

完成整个设计后,设置仿真时间,开始仿真。设置Simulik的仿真停止时间为2 000,仿真步进设为自动。仿真结果如图3,图中前两栏为正交波信号,最后一栏为QPSK已调信号。

图3 QPSK仿真波形

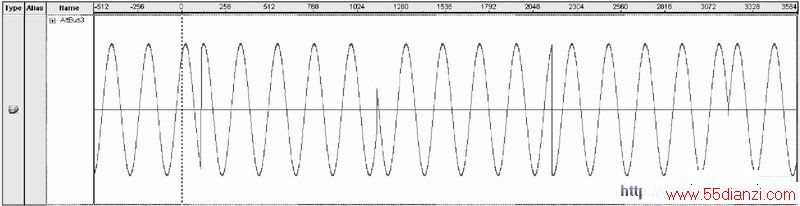

3.2 硬件测试

在Simulink中完成仿真验证后,需要把设计转到硬件上去实现。这是整个DSP Builder设计流程中最为关键的一步,可获得对特定FIGA 芯片 的VHDL代码。双击QPSK模型中的SignalCompiler,点击分析按钮,检查模型无错误后,打开SignalCompiler窗口,在图中设置好相应项后,依次点击1、2、3 3个按钮,逐项执行VHDL文件转换、综合、适配,即可将。mdl文件转换为.vhd文件。同时,在工作目录生成的文件中有tb_qpsk.tcl和tb_qpsk.v文件.tb_qpsk.v文件是在QuartusII中要用到的工程文件,tb_qpsk.tcl文件是要在Modesim进行RTL级仿真用到的测试代码。仿真完成后,在QuartusII中指定器件管脚、进行编译、下载。最后进行硬件的下载,连接好FPGA开发板即可。本文采用的硬件是Cyclone系列芯片 EP2C35F672C6N 。图4是在QuartusII中QPSK的已调波形,与仿真波形基本一致。由图可以看出,有4个相位跳变点,正确地反映了QPSK调制的特点。

图4 QPSK的已调波形

4 结论

本文利用了现代DSP技术的功能,在Simulink的环境下实现了QPSK的建模,给出了具体模型,从而避免了VHDL程序的编制,缩短了周期,提高了效率。采用该法,极大地提高了电子系统设计的灵活性和通用性。仿真结果和硬件实现都验证了该方案的正确性。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术