数字直放站中CPRI协议的FPGA实现

点击数:7642 次 录入时间:03-04 11:33:32 整理:http://www.55dianzi.com DSP/FPGA技术

0 引 言

随着移动通信的发展。通信网络覆盖范围已经成为衡量通信网络运行的重要标准,直接影响着运营商的经济效益。而直放站的发展应用,已成为提高运营商网络质量,解决网络盲区或弱区问题,增强网络覆盖的主要手段之一。一个基站可以与几个直放站相连,可以组成链状、星型、树型等灵活的拓扑结构,使基站的覆盖范围大大增加。同时,既节省空间,又降低成本,提高了组网的效率。

但由于传统模拟直放站设备间没有统一的协议规范,无法满足系统厂商与直放站厂商的兼容,无法实现基站和直放站之间更有效的互通,从而限制了两者之间控制和数据的可靠传输。2003年6年,由包括爱立信、华为、NEC、北电网络及西门子5大集团合力制定了CPRI(Common PublIC Radio Interface)接口。该组织成立的主要目的是制定这个接口的标准协议,从而使该接口成为一个公共的可用的指标。开放的CPRI接口为3G基站产品和2G数字直放站在增加效益,提高灵活性方面提供了便利。

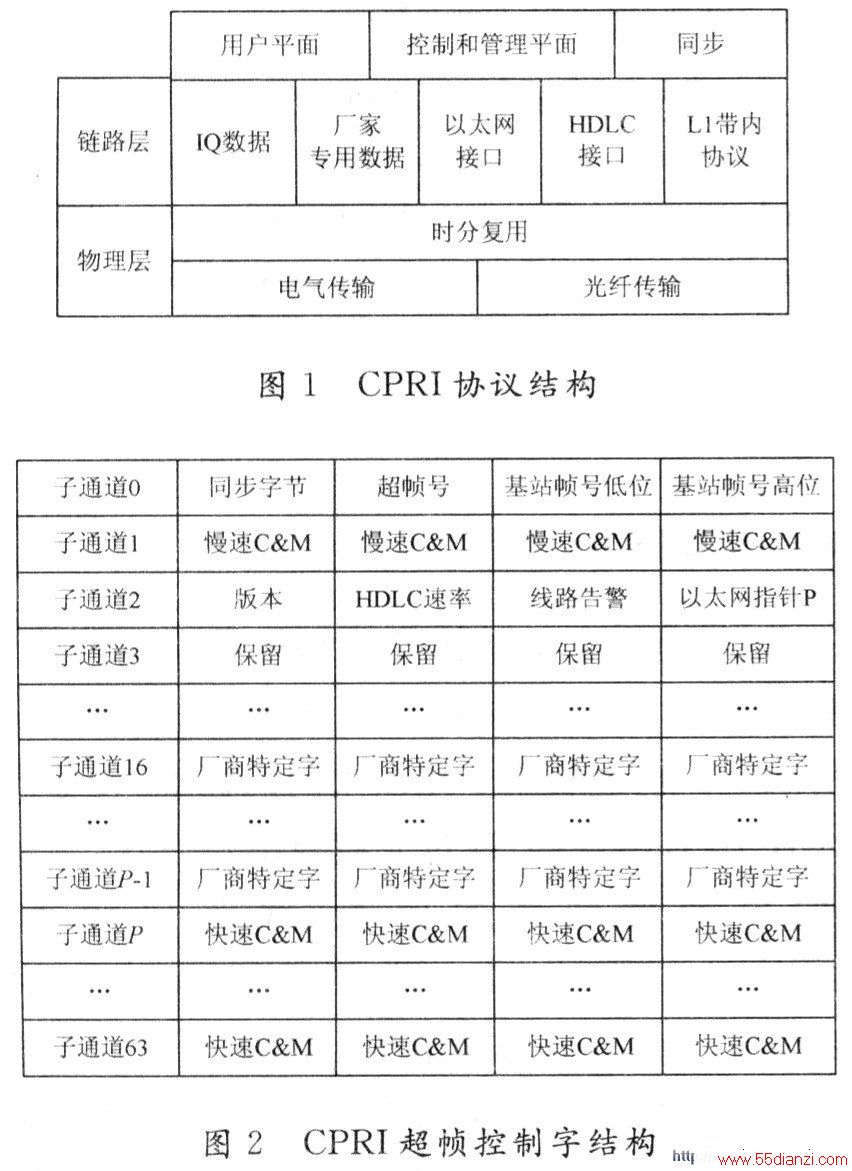

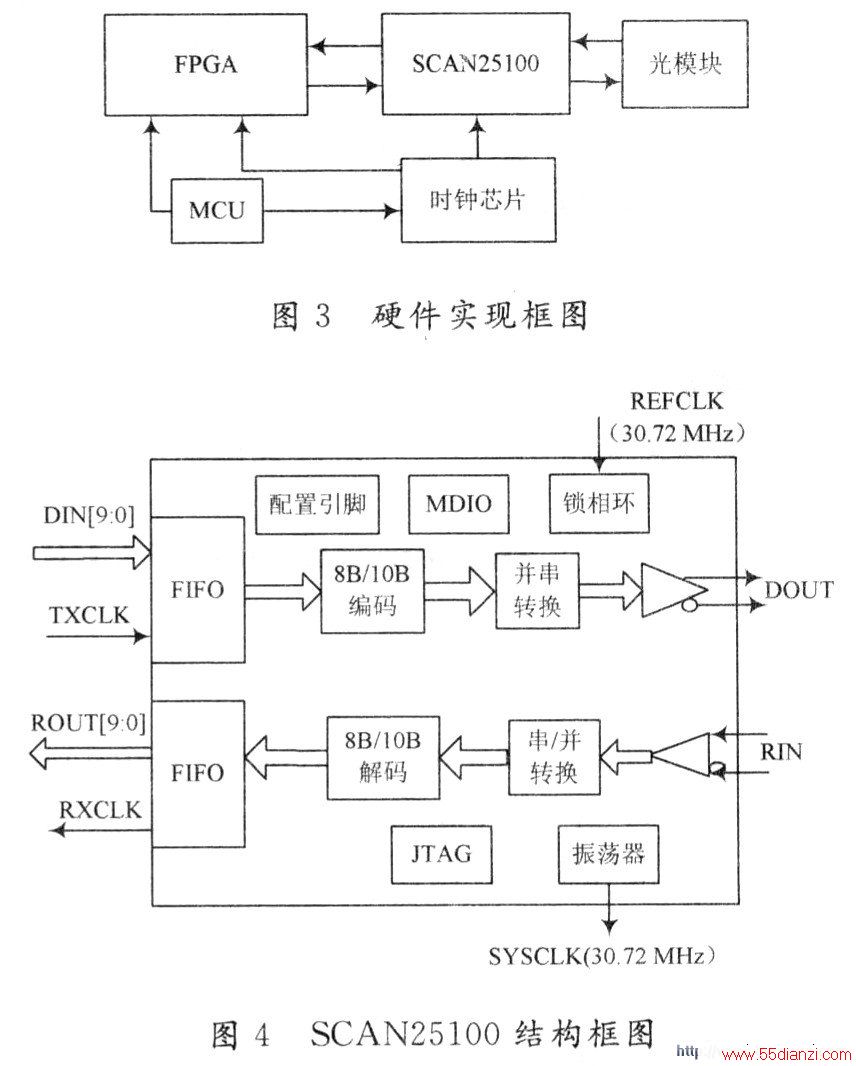

1 CPRI协议概述 CPRI规范定义了物理层和链路层两层协议,能实现数字基带IQ信号传输时分复用,其协议结构图如图1所示。物理层用千兆以太网的标准,传输的数据采用8 B/10 B编解码,通过光模块串行发送,为达到所要求的灵活度和成本效益,线路比特速率有614.4 Mb/s,1228.8 Mb/s和2 457.6 Mb/s三种。链路层定义了一个同步的帧结构。帧结构包括基本帧和超帧,每个基本帧的帧频为3.84 MHz,包括16个时隙,根据线路比特率的不同,每个时隙的大小分别为1 B。2 B,4 B。其中第一个时隙为控制时隙,其余15个时隙为I/O数据时隙,用来传送I/O数据流。超帧则由256个基本帧构成,256个基本帧的控制时隙共同构成超帧的控制结构(如图2所示),同时,定义了快速C/M通道(以太网)和慢速C/M通道(HDLC),用于传送控制类和管理类的数据,可以对直放站进行维护。

2 硬件实现方案

2.1 方案对比

对于CPRI硬件实现方案,有以下几种方案可以选择:

(1)PMC方案。采用PMC7830或PMC7832芯片,这一类芯片把CPRI协议全部集成在芯片内部,只留出接口,使用简单方便,可完全支持用于无线基站连接的公共射频接口(CPRI)规范。

(2)用带ROCKET IO的FPGA实现CPRI协议,此方法灵活性高,但开发时间周期会比较长,影响产品开发。

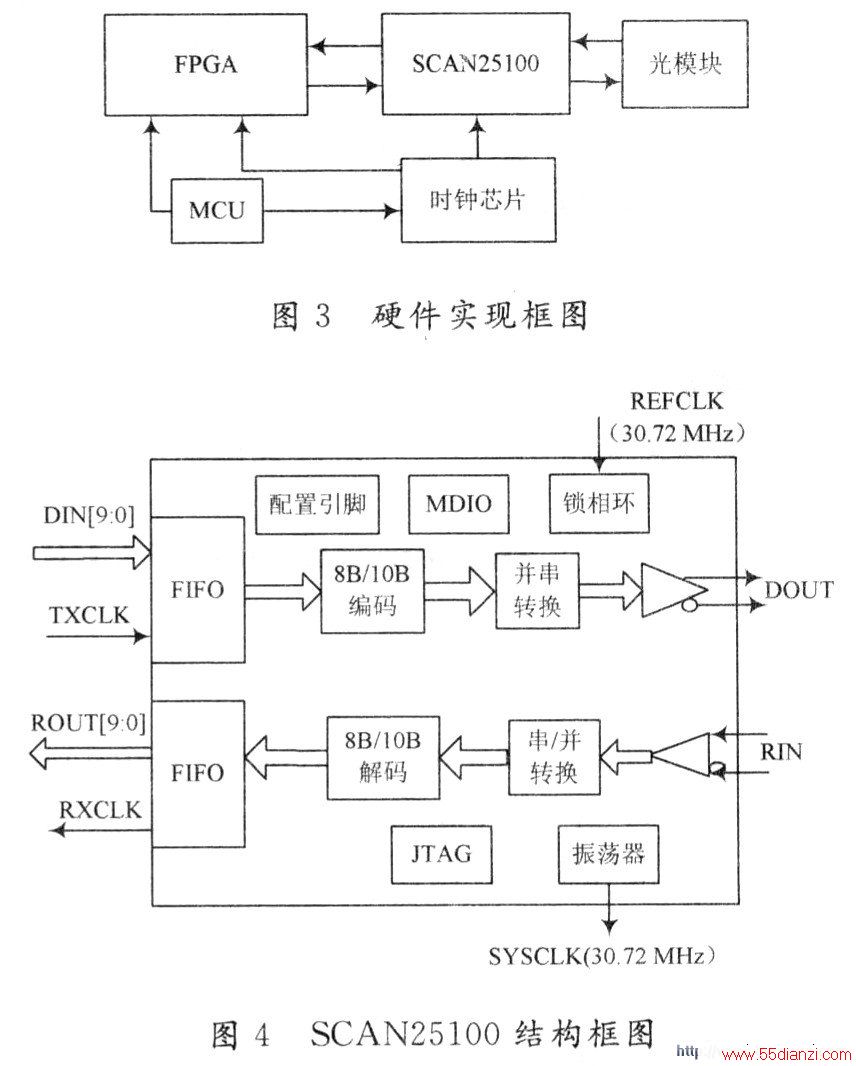

(3)FPGA与SCAN25100相结合。由FPGA实现CPRI的成解帧及相关接口设计,SCAN25100负责完成8 B/10 B编解码和高速串并转换。链路层的帧协议修改方便,而物理层则由芯片完成,使用简单,性能稳定。开发成本较低,且扩展性好。

(4)FPGA与TLK4015相结合。TLK4015是4通道、0.6~1.5 Gb/s通道收发器,当系统需要多的通道数时,使用该方案可以减少电路板尺寸。

2.2 硬件详细设计

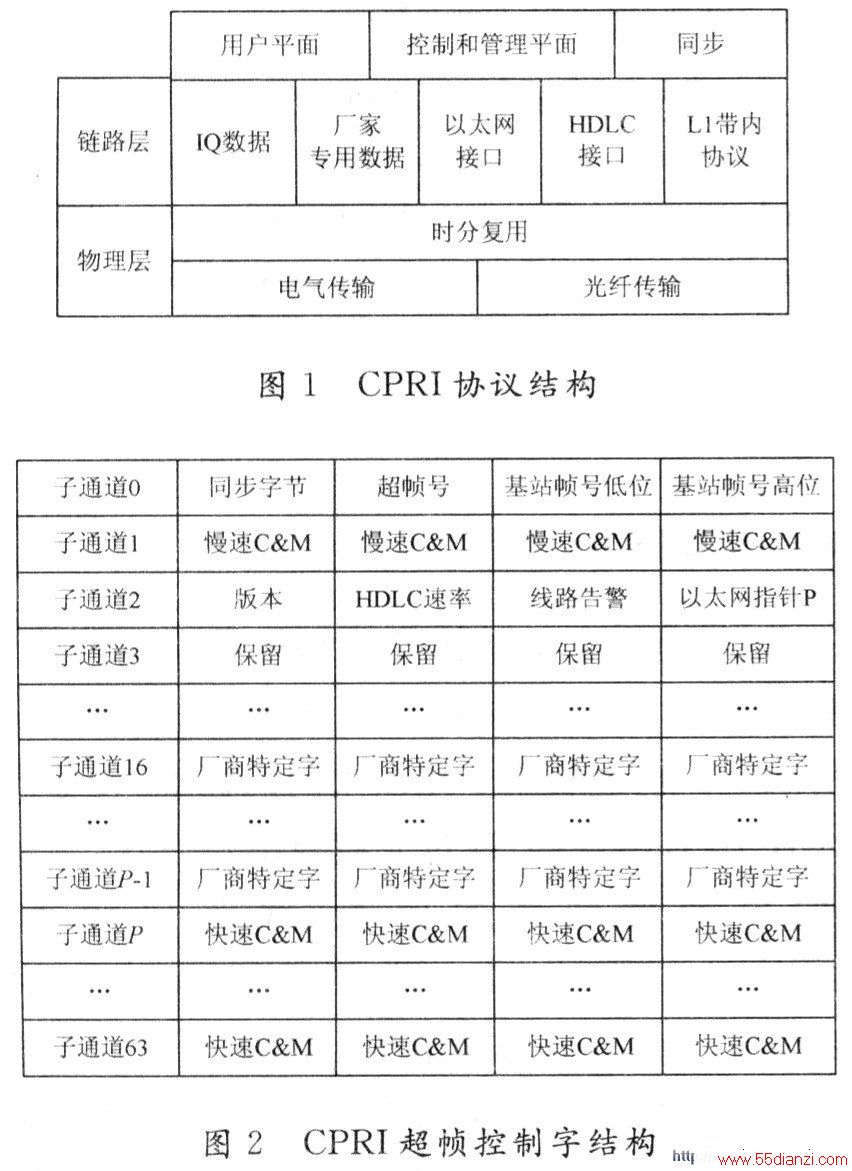

该设计采用第3种的硬件实现方案,整个硬件实现由5个部分组成,如图3所示,分别为CPRI链路层协议实现模块,CPRI物理层协议实现模块、光传输模块、时钟管理模块和系统配置与监控模块。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术