1引言

随着软件无线电技术的发展,传统的基于复杂模拟硬件的接收设备逐渐向数字IC产品过渡,而FPGA作为ASIC产品原型设计的可编程逻辑器件,以其丰富的逻辑资源和可重新配置的优势,成为人们前期研究与开发的重要手段。因此,在可编程逻辑器件上实现数字扩频接收机关键技术进行研究,具有重要的应用价值。

本文给出了一种数字差分BPSK直接序列扩频接收机的方案,并通过simulink进行了仿真,同时本文深入探讨了方案中的关键技术在FPGA中的实现结构,在保证系统稳定性,和不影响系统性能的前提下降低硬件复杂度的问题上提出了FPGA实现方案,并最终在Xilinx XC2V500 FPGA上实现了整个系统,对工程实践有一定的指导意义。

2. 数字差分BPSK扩频接收机的结构与实现

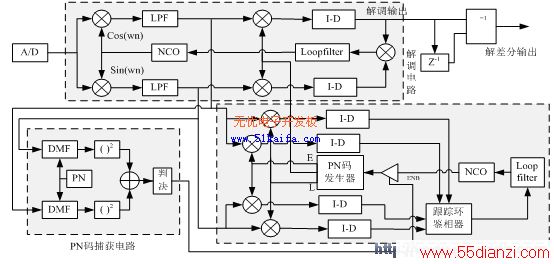

数字BPSK扩频接收机原理图见图1,系统主要可以分为三个部分:解调电路、PN码捕获电路和PN码跟踪电路。

图1 数字差分BPSK扩频接收机原理图

*本文工作得到国家自然科学基金资助(批准号:60171037)

本文关键字:接收机 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:基于FPGA的FSK加密通信