5 本文作者创新点

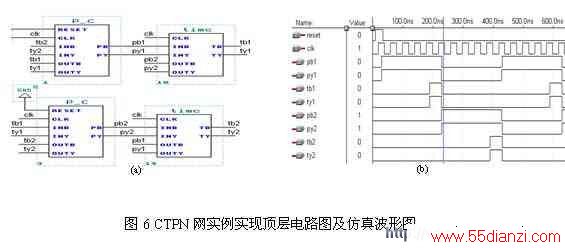

本文给出了几种Petri网系统的硬件实现方案,采用VHDL语言分模块实现,描述元件的功能并将元件存入WORK库中,使设计具有很强的可读性、可重复性、及可修改性,大大提高了系统的开发效率。

参考文献

[1] R. 大卫、H. 奥兰 著,黄建文、赵不贿译。佩特利网和逻辑控制器图形表示工具[M],北京:机械工业出版社,1996

[2]赵不贿,景亮,严仰光。Petri网的硬件实现[J],软件学报,2002(10):1652-1658

[3] Naehyuck Chang, Wook Hyun Kwon, Jaehyun Park. FPGA -based Implementation of Synchronous Petre Nets, Industrial ElecronICs, Contorl and Instrumenation,1996,Proceed.

[4] 祝习兵,胡健生,黄金志。基于CPLD的基本Petri网系统的硬件实现[J],现代电子技术,2004(3):102-105

[5] 赵不贿,严仰光,陆继远,唐平. 控制电路基于Petri网的图形化设计与仿真研究[J],电路与系统学报,2005(5):54-58

[6] 沈宪明,白瑞林,章智慧. 基于FPGA的模糊CMAC网络的硬件实现[J]. 微计算机信息, 2006, 2-2: 基于FPGA的模糊CMAC网络的硬件实现

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:VHDL编码中面积优化探讨