引言

随着我国 铁路 客运专线、高速铁路建设步伐的加快,研究开发以一体化、网络化、数字化为典型技术特征的新型列车信号控制系统成为必然趋势。

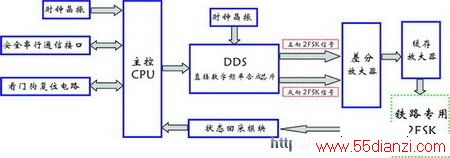

通过研究 DDS 直接 数字频率合成 技术生成铁路专用2FSK(二进制频移键控)调制信号的新方法,论证了新型列车信号控制系统的信息发送单元数字化实现的可行性,并完成了相应的软、硬件设计。实验和工程应用结果均表明,该设计的精确度和稳定度完全可以满足铁路现场应用的要求。

我国铁路 2FSK信号 的理论分析和数学建模

当前我国铁路 信号系统 的主要信号制式包括3种,不同系统信号特征的异同点如表1所示。

2FSK信号数学表达式为[1]:

其中S(t) 是2FSK信号的基本表达式,g(t) 是相位变化量子式,AS为2FSK信号时域幅度,f0为2FSK信号中心频率,f(t)为低频调制信号,Kf为最大载频偏移量。

从公式(1)及(2)中可以总结出,2FSK信号数学基本原理简单来说就是利用数字基带信号f(t)引起的相位变化量g(t)去调制载频信号f0,控制上边频fh和下边频fl的切换,实现数字基带信息的传输。根据对边频切换时机的不同,2FSK调制又分为相位连续方式和相位不连续方式。

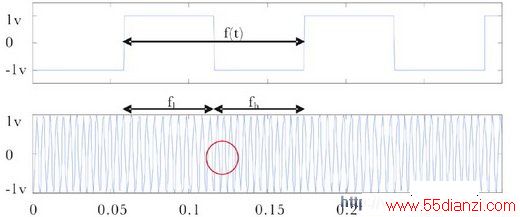

在这些不同信号制式中,除了所采用的调制方式相同外,它们还具有铁路信号所特有的共性:即低频调制信号f(t)为方波方式,依靠方波频率的变化,实现列车不同速度等级的编码。由于铁路2FSK调制信号的通频带、低频调制信号有着极其严格的限定,有别于民用通信领域常规信号。在认真分析我国铁路主要信号制式的典型参数特征的基础上,利用MATLAB仿真软件在计算机上可以建立我国主要信号制式传输信号的数学模型[2],其典型时域波形的仿真图形如图1所示。

图1 我国铁路2FSK信号仿真波形

通过公式(1)和(2),可以抽取出我国铁路专用2FSK信号的典型参数特征,即:数字基带信号f(t)、上边频fh、下边频fl。

图1显示了三个典型参数之间的特定依存关系:即一个完整周期的数字基带信号f(t)包含了持续时间分别为1/2周期的上边频fh和下边频fl信号,并且两者在切换的瞬间保持了相位连续的特征,如图中圆圈中所示。在MATLAB仿真环境下,通过动态改变三者的特征值,可以模拟实现我国铁路主要信号制式的全部信号模式。

DDS技术方案

基于对DDS技术深入研究,DDS技术应用在新型列车信号控制系统是完全可行的,技术方案可以简要归纳如下:

DDS的数学模型

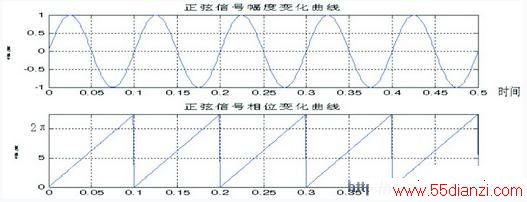

根据傅立叶变换理论,任何周期信号都可以分解为一系列正弦或余弦信号之和,对于一个频率f固定的周期性模拟或数字信号而言,无论其幅度如何变化,在每一个时间周期内,信号相位角按照固定角频率w线性变化。如图2 MATLAB仿真波形所示。

图2 信号幅度与相位变化的对应关系

在一个系统时钟周期内,正弦信号相位的变化由下式决定:

![]() (3)

(3)

假定时间间隔dt以系统时钟周期1/fcLOCk(可以看作为采样周期)来代替,可得:

![]() (4)

(4)

式中Dphase:采样时间间隔内信号相位的增量。

从公式(4)中显而易见,控制Dphase的变化,就可以控制不同的频率信号的输出。把0~2的连续相位量化为0~2N位数字相位,则Dphase可以表示为:

![]() (5)

(5)

式中N为DDS相位寄存器位数(通常为24~32);M为DDS相位寄存器的步长。

根据公式(5)和公式(4),推算出:

![]() (6)

(6)

公式(6)表明在系统时钟(DDS的参考频率源)保持恒定的条件下,通过改变预置的频率控制字(相位累加器的步长M),就可以精确控制输出信号的频率变化。

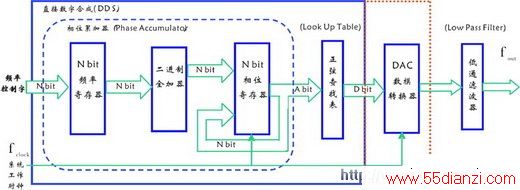

DDS硬件架构

图3显示DDS硬件架构主要由相位累加器、正弦查找表、模数转换器以及低通平滑滤波器等部分构成[3]。

图3 DDS硬件架构框图

相位累加器在DDS功能实现上发挥着核心作用,把0~2的连续相位转换为32位的数字相位(假定相位累加器的位数N=32),在时钟脉冲的控制下,输入到频率寄存器的控制字在相位累加器中定期累加转变成为输出信号的数字相位信息。

正弦查找表是一个存储了特定数据的只读存储器。正弦查找表中固化了对一个满周期标准正弦信号以系统时钟频率为采样频率,采样点数为2N(N:相位累加器位数)的波形取样值(二进制编码)。

DDS中的数模转换器用于把正弦查找表输出的正弦信号数字幅值转换为模拟幅值。

低通平滑滤波器可以滤除DDS系统时钟引入的高频干扰以及由于DDS内部相位累加器输出相位需要截断固有特性导致的加性相位噪声。

www.55dianzi.com

硬件设计

图4 系统硬件

选用ATMEL 精简指令集AVR MEGA128芯片。主要完成与上位中央逻辑控制单元的双向高速安全串行数据通信,实现列控信息的差错控制和数据帧打包成型;基于对列控数据软件判断处理,以基带调制信号周期为间隔,动态刷新 DDS 芯片控制寄存器,直接实现正弦形式的 铁路 2FSK信号 正/反向双路输出,供给后级差分放大器使用。完成输出信号的状态回采、闭环检查,以校核输出2FSK信号的关键参数指标是否达标。

通信接口主要由Philips SJA1000及外围电路构成。主要完成上位逻辑控制单元与主控CPU之间安全数据交换,接口协议灵活。实际应用中采用了双重冗余的CAN总线方式,确保数据交换安全可靠。

外置硬件看门狗选用MAX1232芯片。主要完成程序由于干扰“跑飞”进入死循环之后,输出复位脉冲,迫使CPU重新从程序原点恢复执行,提高系统的抗干扰能力。

选用AD7008 DDS芯片及外围元件构成。DDS芯片被设置成FSK工作模式。在FSK模式下,其输出信号频率是频率控制寄存器(FCR)0、1以及FSK控制输入引脚FSELECT状态的函数。当FSELECT引脚为低电平时,输出边频f1(FCR1控制),当FSELECT引脚为高电平时,输出边频f2(FCR2控制),只要 严格遵循铁路2FSK信号基带调制信号与边频信号频率依存关系,选择适当的边频频率,并且利用基带调制信号控制FSELECT引脚电平状态即可实现。根据DDS的特点,边频的切换是瞬时完成的(ns级),并且新的输出频率相位累加起点是前一频率的相位累加终点,因此可以保持频率切换点的边频相位连续性,符合铁路2FSK信号的技术特点。关于频率控制寄存器设置数值,可以根据公式(6)确定。

本文关键字:技术 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术