本文提出了一种EPON系统核心 MAC控制器 的设计方案,融合 FPGA 技术与嵌入式系统实现了EPON的点对多点MAC接入功能.帧校验、加密、分类及仲裁等控制部分用FPGA完成.

涉及复杂算法的注册与动态带宽分配利用嵌入式Linux平台实现.对MAC控制器设计中的关键技术点进行了全面阐述,提出了一种基于滑动窗机制的动态带宽分配方案以改善网络QoS性能.系统仿真结果表明,该设计方案可以采用低成本的FPGA来实现,为开发MAC控制器专用芯片提供了实用参考.

近年来随着传输技术和交换技术的不断进步,核心网已经基本实现了光纤化、数字化和宽度化,而传统的接入网仍然是采用电缆传输的模拟系统,两者在技术上的巨大差距导致接入网成为全球信息高速公路的瓶颈.目前尽管出现了一系列解决这一瓶颈问题的技术手段,如双绞线上的xDSL系统、同轴电缆上的HFC系统以及五类线上的LAN,但都只能算是一些过渡性解决方案,不能满足视频点播、家庭购物、数字高清晰度电视播放等新业务对宽带通信的需求,唯一能够从根本上彻底解决接入瓶颈的长远技术手段就是全光接入网.基于以太网的无源光网络(EPON)就是这一背景下应运 而生的光纤接入技术.EPON与传统以太网的主要区别在于传统以太网是点到点(Peer-to-Peer,P2P)的对等网络,而EPON是点到多点(Point-to-Multipoint,P2MP)的主从网络,其技术创新就在于点对多点MAC接入控制的设计与实现.本文提出了一种EPON系统MAC控制器的设计方案,详细阐述了采用包含嵌入式CPU的FP2GA开发MAC控制器的设计全过程,并通过系统软、硬件仿真验证了该设计的可行性,为我国开发MAC控制器专用芯片提供实用参考.

EPON系统结构

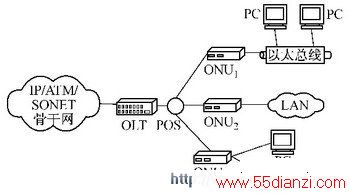

如图1所示,一个典型的EPON系统主要由三部分组成,即光线路终端(OLT)、无源光分路器(POS)和光网络单元(ONU).其中OLT位于局端,一般放在中心机房(Central OffICe,CO),ONU位于用户端,POS连接OLT和ONU,它的功能是分发下行数据和汇聚上行数据.从OLT到ONU的方向为下行方向,反之为上行方向.OLT上行链路与各业务节点相连,ONU下行链路则与各用户终端设备连接.

图1 EPON系统架构

在EPON中,从OLT到多个ONU的下行数据传输过程与从多个ONU到OLT的上行数据传输过程有本质的区别,如图2所示.下行数据采用广播方式以变长以太包的形式从OLT发给多个ONU,每个以太包带有标识目标ONU的逻辑链路标识(LLID),通过识别LLID判断信息包是发给某个或多个ONU的.当数据流到达ONU时,ONU只提取发给它的信息包而丢弃发给其他ONU的信息包;而上行数据则采用时分多址接入(TDMA)技术,每个ONU都分配一个传输时隙,所有时隙保持同步,彼此间留有间隙,保证不同ONU的数据包汇聚到公共光纤时不发生相互碰撞.

图2 EPON的上、下行传输机制

OLT系统设计

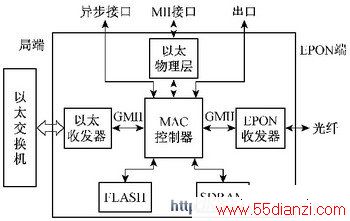

为支持EPON的协议栈结构和工作模式,本文采用图3所示的OLT系统设计,它主要由MAC控制器、EPON千兆位突发光收发器、存储器和外围接口电路组成.其中MAC控制器是采用ALTEra公司的EXCAL IBUR-ARM系列FPGA(带ARM9硬核)芯片实现.在CO端,OLT通过标准的千兆以太收发器与上层交换机相连;在EPON端,OLT通过专用的光收发器连接PON网络.

图3 OLT系统总体框图

该系统可以实现以下功能:

(1)以广播方式向ONU下行发送以太数据包,以TDMA方式接收来自ONU的以太包;

(2)发起并控制ONU的注册过程,根据用户的QoS要求为ONU分配带宽;

(3)除了网络的汇聚和接入功能,OLT还提供OAM功能.

核心MAC控制器的实现

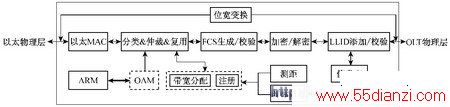

图4所示为本文设计的EPON系统核心MAC 控制器的功能框图,它由硬件和软件部分组成.硬件部分(图中实线表示的模块)由FPGA来完成[3],实现点对点仿真,以太帧的校验、加/解密、分类/仲裁/复用等控制功能;软件部分由嵌入式系统Monta Vista Linux来完成对ONU的注册和动态带宽分配(DBA).

首先对图中各模块的功能作一简要说明.位宽变换模块实现数据流的8bit位宽(字节为单位)与32bit位宽(双字为单位)之间的互换;LLD添加/校验模块主要完成LLD的添加/校验;分类/仲裁/复用模块实现对以太帧的分类、发送优先级仲裁和复用;测距模块计算ONU至OLT的往复时间(RTT),以便进行上行时延补偿.时标处理模块实现OLT与ONU的时钟同步.下面就MAC控制器在软、硬件设计中涉及到的关键技术进行全面阐述.

图4 核心MAC控制器功能框图

位宽变换及时钟设计

考虑到EXCAL IBUR-ARM系列 FPGA 内嵌的ARM922T是一款RISC架构的32bit微处理器,为了方便FPGA与微处理器之间的数据交换, MAC控制器 的内部数据统一采用双字为单位进行处理.OLT与ONU之间的线路传输速率是1.25Gbit/s,码流在物理层经过串/并变换、8B/10B编码之后的速率为125Mbit/s,而进行位宽变换后,FPGA的工作频率下降到31.25MHz.本文设计FPGA开发板时,采用了25MHz的晶振作为时钟源.

值得一提的是,位宽变换模块需用到125MHz和31.25MHz2个时钟(分别由倍频器和分频器提供).输入的8bit码流以125MHz的频率顺序写入4个FIFO中,同时以31.25MHz的频率从这4个FIFO中并行输出,直至一帧结束.但必须考虑数据帧的帧长(以字节为单位)不能被4整除的情况,如最后只剩下3个8bit码.这时将‘0x00’写入最后的空闲FIFO中,使帧长满足4的整数倍.为此,位宽变换模块增加了以字节为单位的帧长和以双字为单位的帧长统计功能,用于告 知其后级联的模块只对帧有效数据进行处理.所有的变换处理均在FPGA内部实现,因而不增加FPGA的外部引脚.

分类、仲裁和复用技术

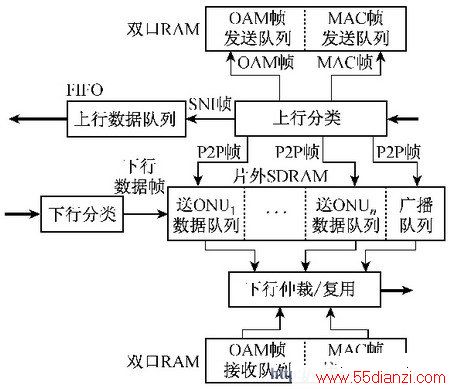

分类、仲裁及复用是MAC控制器最为关键的功能,FPGA与微处理器如何进行数据交换、数据流如何分类及缓冲、何种仲裁机制能够实现信道的最佳复用等技术细节都是模块设计时必须考虑的问题.上行分类器收到以太帧后,首先根据帧类型(Type域)区分MAC帧、OAM帧和数据帧.如果是MAC帧或OAM帧,则直接写入双端口RAM的MAC帧队列或OAM帧队列,同时给出相应的中断请求信号,通知ARM来处理;如果是数据帧,区分是发往核心网的SNI帧,还是送给其他ONU的P2P帧.SNI帧按照FIFO机制送往上层交换机;P2P帧则写入SDRAM中,直接参与下行数据帧的仲裁和复用.图5给出了帧分类、仲裁和复用处理流图.

图5 帧分类/仲裁/复用处理流程图

图中,下行仲裁/复用器首先对送给同一个ONU的数据帧(包括下行帧和P2P帧)、OAM帧和MAC帧进行优先级仲裁,MAC帧优先级最高,数据帧次之,OAM优先级最低.然后要为发往不同ONU的帧优先级进行二次仲裁,最终通过一条物理链路将这些帧以时分复用送出去,所以下行帧和P2P帧必须先缓存在SDRAM中,等待发送指示信号.将SNI帧放在SDRAM中也是可行的,但由于上行信道的带宽分配过程已经实现了对帧的优先级仲裁,所以本文选择用FIFO替代SDRAM,完成对SNI帧的缓冲,这样可以大大减少FPGA芯片的外部引脚,降低了ASIC芯片的制造成本.

安全策略

在EPON系统中,各个ONU的上行通道是彼此独立的,用户无法窃取他人的信息;下行方向是媒质共享网络,数据以广播形式发送,每个ONU都能接收到所有的下行数据,802.3ah引入LLID来限制每个ONU只能接收属于自己的数据包.然而用户可以通过某种方式绕开LLID校验,窃取其他ONU的信息,最为典型的解决方法就是在下行方向对所有的数据帧进行加密传输.事实上,这种加密方式存在许多安全隐患.首先,未经加密的下行MAC帧和OAM帧如果被成功获取的话,入侵者便可以轻易掌握其他用户的关键信息,如ONU的LLID和终端用户MAC地址,进而在上行方向通过盗用LLID和MAC地址来窃取其他用户的带宽;其次,在上行方向合法用户可能通过伪造MAC帧或OAM帧,来更改EPON系统配置,甚至侵入电信管理网络,扰乱整个电信网.针对这两种威胁,本文采用了一种加密与认证相结合的安全策略.

信息加密

加密算法本文采用的是AES算法,密钥长度选取128bit.下行方向OLT对所有类型的帧进行加密,加密区域从目的MAC地址到FCS域.密钥由ONU产生,上行发送给OLT,不可能被用户截获,不同的ONU使用不同的密钥,从而保证了下行数据私密性的要求;上行方向,为了防止假冒用户,ONU对MAC帧和OAM帧进行加密,加密区域也是目的MAC地址到FCS域.

本文关键字:控制器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:精确综合:下一代FPGA综合平台