�����������г����кܶ���� DSP оƬ��ģ���ϵͳ��Ŀǰ, DSPоƬ����ļ��������ж���Ҫ�����ڷ�����,��DSP�������۸��、�����,��ʹ�ô������г�ϵͳ�ĵ��Ժܲ�����;����Щ����DSPоƬ��ϵͳһ�������������ֻ��������ǰ����ĵ�һ�ij���,Ҳʹϵͳ��������ܵ��˺ܴ�����ơ������о���DSPоƬ������صĻ���ԭ��,��������Щԭ��,���� CAN���� ,ʵ����DSPоƬ����� �ܿؼ��� ,ʹ��DSPоƬ����ļ�����������ֱ���ܿ�����λ���ػ����������ػ�������Ժܴ�,�������г�ϵͳ�ڵ���ʱ�Ϳɸ�����Ҫ�����ϸ�������ģ�������DSPоƬ���ز�ͬ�ij���,����������������,�dz�������

����1 CAN���ߵ��ص㼰����ԭ��

����CAN Control Area Network,��������������������һ����Ч֧�ֲַ�ʽ���ƻ�ʱ���ƵĴ���ͨѶ��������˫���ķ�ʽ������һ���ڵ㷢����Ϣ ����ڵ������Ϣʵ����ȫ�ֲ�ʽ���ϵͳ����������������д���Ŀɿ��ԡ���ṹ��ʽ��ͼ1��ʾ��CAN���ߵ���Ϣ��ȡ�����˹㲥ʽ�Ĵ�ȡ������ʽ��Ϣ�������κ�ʱ�����κνڵ㷢�͵����е�������ÿ���ڵ��CAN���߽ӿڱ�����������ϳ��ֵ�������Ϣ����˸��ڵ㶼������һ�����ռĴ����üĴ���������Ϣ Ȼ�������Ϣ���ķ������Ƿ��ȡ��Ϣ���е��������ж��Ƿ�ʹ����һ��Ϣ�� CAN���ߵ��ص�����ͨ�����ݿ������洫ͳ�ĵ�ַ���� CAN��������������ݶ����ǽڵ����ַ�ʽ���ŵ��ǿ�ʹ�����ڵĽڵ�����������ϲ������Ƽ��������豸��Ӱ������ϵͳ�Ĺ���������CAN���ߵĸ���ϵͳ���Ը����û���Ҫ����ı�ڵ�������CAN�����շ����ݵij������Ϊ8���ֽ����������ռ��ʱ��������Ա�֤ͨ�ŵ�ʵʱ�Ԣ�ͨ��������߿ɴ�1Mb/s����Ϊ40m ��Զ�ɴ�10km����Ϊ5kb/s ����ͨ�Ž��ʵ�Ҫ��ϵͿ����ǹ��˻�ͬ���������˫���ߡ�

����2 DSPоƬ�ij������������ԭ��

�����ڱ������,DSP�ij������������������ͨ������HPI 8λ���пڵIJ���ʵ�ֵġ������ȼ���һ��DSP��HPI 8λ���п��Լ���ζ������ж�д����,Ȼ����ܱ����о�������DSP������ؼ�����

����2.1 DSPоƬ�IJ���(HPI)���

����HPI���пڵĶ�д������Ҫ��DSP������16λ�Ĵ�������,���Ƿֱ���:HPIC HPI Control Register,���ƼĴ��� 、HPID HPI Data Register,���ݼĴ��� 、HPIA HPI Adress Register,��ַ�Ĵ�����дHPIC�Ĵ�������HPI���ڵĶ�д��ʽ�Լ����ݸߵ��ֽڵĶ�д˳���;дHPIA�Ĵ�������д���������ݵľ����ַ(����ģʽ��2 Ϊ����д��/����ʱ�ij�ʼ��ַ);��HPIDֱ��д��/�������ݡ�

����HPI�����ֶ�д��ʽ:��ͨģʽ�µĶ�д����HPIA�ĵ�ַ��HPID������д���ڴ�õ�ַ�����ݶ���HPID;����ģʽ��HPIA������ַ,ÿ�ζ���д�������������Զ�ָ����һ������д�ĵ�ַ��

����2.2 DSPоƬ�ij������������

������CCS���������ɵ�DSP��ִ���ļ���һ��.out�ļ��������������ȵ���TI��˾�ṩ��hex500.exe����,����ת��Ϊ.hex�ļ�3,����.hex�ļ�����֯�ṹ��������: ����һ��һ���Ŀ�(bLOCk)���,ÿһ����ĵ�һ���ֽڱ�ʾ��ǰ������Ĵ����ص���Ч���ݵij���,�ڶ�、�������ֽڱ�ʾ��Щ��Ч����д��DSP�ڴ�ʱ����ַ,�ӵ�����ֽڿ�ʼ�Ǵ�д��DSP�ڴ����Ч����(���ĸ��ֽ�ͨ��Ϊ0x00,����Ч����),������ǰ��Ч���ݳ��ȵ����ݲ���Ҫ��������Ҫע�����,�ļ��Ľ�β(Ҳ�������һ����)�ĵ�һ���ֽڵ�������0,��ʾ��ǰ��Ϊ�ļ��Ľ�β,�����κ����ݶ�����Ч���ݡ�֪������.hex�ļ�����֯�ṹ��,�Ϳ��Է�������е���Ч����,Ȼ��Ϳɽ���Щ��Ч����д��DSP���ڴ档��������ͨ��DSP��HPI�������д�����ġ���������: ���ȶ�DSP��λ,���ԭ��������;Ȼ���ڵ�Ƭ���Ŀ����´�.hex�ļ�����ÿ��д��ij�ʼ��ַ,����Щ��ʼ��ַ��ʼ���ϵؽ���Ч����д��DSP���ڴ�;д������ɺ�,��DSP���ڴ��ַ0x007fд����0x8000,��������,��ʼִ�С�

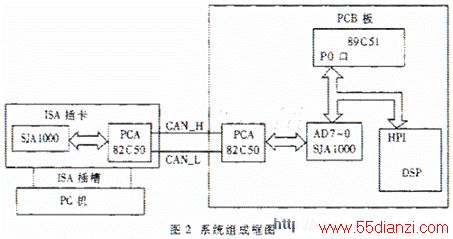

����3 ϵͳ�����

����ϵͳ��ɿ�ͼ��ͼ2��ʾ�� ISA�忨ͨ��ISA�����PC��(���൱�ڴ�����ϵͳ�ϵ����ػ�)����,��PC���Ŀ���,��������PC��������,��PC��ת���յ������ݡ��忨���� SJA1000 оƬ,ͨ������PCB���ϵ�SJA1000ʵ�����ݽ�����

����CB���ϵ�SJA1000������/��ַ�ź����뵥Ƭ����P0��������,ͬʱP0����Ҳ��DSP��HPI����������HD0~7�������ڵ�Ƭ���Ŀ�����,SJA1000��������PC��������,������ͨ��P0���ڷ�����Ƭ��,Ȼ��Ƭ���ٽ���Щ����ͨ��HPI����DSP��

www.55dianzi.com

����4 ϵͳ��ʵ��

����4.1 Ӳ��ʵ��

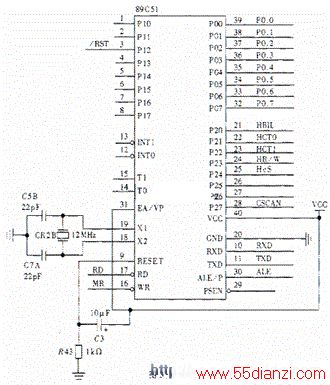

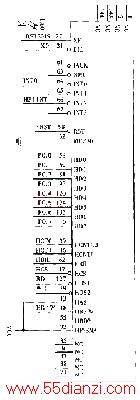

��������ϵͳ��ɿ�ͼ,��������ģ���Ӳ��ʵ����ͼ3、ͼ4、ͼ5��ʾ��ͼ3Ϊ��Ƭ���Ľӿڵ�·,����P0�� SJA1000 �IJ������ݿ�D0~D7(��ͼ4��ʾ)�� DSP ��HPI��(��ͼ5��ʾ)����,ʵ�����ݽ���:SJA1000�������� CAN���� ������,ͨ���������ݿ�D0~D7��P0�ڷ�����Ƭ��,��Ƭ�����յ����ݲ�������������ͨ��P0�ں�HPI��ת����DSP�� HBIL、HCT0、CHT1、HR/WΪHPI�ڵĿ����źŤ�2��,��HPI�Ķ�д�Ȳ������ܿ��ڵ�Ƭ���� CSCANΪSJA1000��ѡͨ�ź�,/RSTΪSJA1000��DSP�ĸ�λ�ź�;RD、WR�ֱ�Ϊ��д�����źš�

����4.2 ����ʵ��

����PC���������.hex�ļ��ķ���,�����ݷ������,ͨ��SJA1000,��ÿһ����ġ�ͷ��������Ч�������������CAN�����Ϸ���,ֱ�������ļ�������Ϊֹ����Ƭ�����Ƴ�������մ�SJA1000�ϴ���CAN�����ϵ�����,�������ݵ�����(����֡�����ǡ�ͷ����������Ч����),Ȼ��ͨ��DSPоƬ��HPI���пڽ���Ч������ȷ��д����Ӧ���ڴ��ַ��

���������о���������ṩ��һ�ּ�����、�ɱ�������DSP������ط�������������и߶ȵĿɿ���、����Ժ�ʵ���ԡ���������ڴ������г�����һ�����ӵ�DCSϵͳ��,�ܹ��ܺõؿ����г����ڶ����DSPоƬ��ϵͳ�ij������,������ض����ǽ��е���,ʹ��Щϵͳ�ܸ��ݲ�ͬ����Ҫִ�в�ͬ�ij���,ȡ���˺ܺõ�Ч����Ŀǰ�Ϻ������Ĵ������г�Ҳ�����˴������ߵ��Լ�����

���Ĺؼ��֣����� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����