在上面各子滤波器参数组中,相邻滤波参数都相隔D个,也将是输入信号x(n)依次通过各子滤波器后产生新的信号u(n),此时的抽样周期TD=1/Dfs,即x(n)通过相邻子滤波器后产生的输出信号间的抽样时间是一个抽样周期1/Dfs。那么,x(n)依次通过子滤波器参数组中相距L相应的子滤波器时产生的输出信号间抽样时间是L/Dfs。这样就能够产生L个延迟样点时间。最后再采取数据抽取工作。抽取工作其实可以采取对未被抽取的输出信号相对应的数据进行内插滤波操作,而不对抽取的输出信号相对应的数据进行内插滤波操作。这样可让DSP减少许多运算操作,节省DSP实现时延过程的执行时间,能够保证信号数据的准确性。选用的DSP芯片是TI公司的TMS320C6416,主频可以达到1 GHz,运算速度已达到8 000 MIPS,为32 b定点数字信号处理器。根据输入信号x(n)的频谱分析可得出最高频率FMax(fmax≤fs/2),其中利用.Matlab或者SystemView软件设计一个低通滤波器,得出滤波系数。

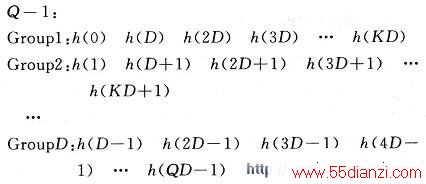

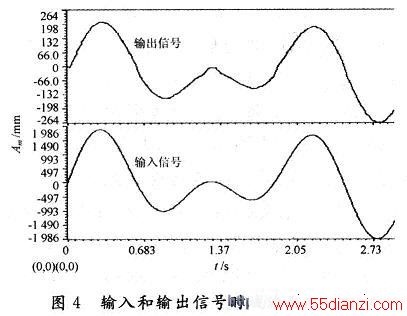

设定一个输入信号x(n)包含f1=6.25 MHz和f2=10 MHz的信号,采样频率fs=25 MHz,要使信号多径时延精度达到1 ns,就要选择内插倍数为40倍。设计一个最高频率10 MHz的低通滤波器,得出含滤波器长度N=800的滤波器系数。将这些系数分为40个子滤波器参数组,每组中含有20个滤波系数,分别依次取子滤波器参数组组名为Group1,Group2,…,Group40。当信号需要延时5 ns时,通过内插后则需要5个采样样点延迟时间,然后再进行抽取实现。在DSP中算法的实现,是将包含f1=6.25 MHz和f2=10 MHz输入信号通过相对应的Group5子滤波器进行FIR卷积。在DSP系统的硬件仿真结果中可以得出输入输出信号时域波形图及其频谱图。图4是输入、输出信号时域波形比较图。

从图4可以看出,在输入信号x(n)经过40倍内插滤波器滤波,并进行40倍抽取实现后的输出信号与输入信号有着相同的时域波形,并且输出信号时域波形相对输入信号时域波形出现了相应的延时。

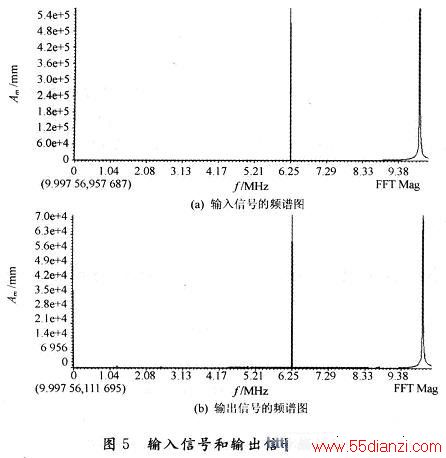

图5为输入、输出信号的频谱图。

在原始采样频率fs为25 MHz下,输入信号x(n)经过40倍内插滤波器滤波并进行40倍抽取实现后,对输入输出进行频谱分析,可以得出输出信号的采样频率仍是25 MHz,并含有两个频率信号,其一信号频率f1=6.25 MHz,另一信号频率f2=10 MHz。从而得出输出信号频谱与输入信号频谱是吻合的,如图5所示。

3 结语

提出了一种实现时延的方法。可以选用大容量存储器作大尺度的延时处理,并选用DSP作插值算法做高精度的小尺寸的延时算法处理。结合软件无线电思想中的内插和抽取技术,重点介绍高精度、小尺寸的信号延时处理方法。它具有DSP处理时间周期短,节省DSP数据存储空间,时延精度高等特点。用实验板SEED-DEC6416进行硬件仿真。试验结果表明,设计结果基本达到要求,该方法的实现过程是可行的。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术