Turbo 码自1993年问世以来,以其出色的性能,在工业和科研领域都引起了广泛的关注。Turbo码性能逼近(信噪比差为0.7dB或更小)由Claude E. Shannon确定的信道容限。Berrou、Glavieux和Thitimajshima最先提出了Turbo码,其结构由两个并行级联卷积编码器组成。Turbo码编码方案产生同一信息序列的两个不同交织形式的分量码。解码时,由两个 MAP解码器 以迭代方式对判决结果进行解码。MAP 解码算法利用接收数据和校验符号(以真实和交织形式的数据计算而来的校验位),以及其他的解码软输出(外部的)信息,得到更加可靠的判决结果。

本文将讨论在ADI Blackfin通用定点 DSP 处理器上如何高效实现Turbo MAP 解码器的技术。

TURBO解码器

在Turbo解码过程中,MAP算法被用于确定最接近传输数据的信息位。MAP算法先对每个传送的数据位计算一个后验概率值(APPs),然后根据最大的后验概率值为该数据位分配一个判决值,再进行解码。MAP 算法使用后验概率值APP计算每一个传送位Cn的最大似然比LLR,使误码率(BER)最小,其计算公式如下:

(1)

(1)

其中,Y1N=[y1,y2,…,yN]。

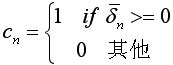

译出的信息位通过以下硬判决得到:

在 UMTS Turbo解码器中,应用一个八状态的RSC编码网格,在n时刻,当输入序列为Y1N时,比特“1”和比特“0”的APP可分别由式(2)和式(3)求得。

(2)

(2)

![]() (3)

(3)

其中,分别是的对数, 是在n时刻和状态m下的前向状态度量, 是n时刻和状态m下的分支度量,是n+1时刻和状态k下的反向状态度量。每级中,只需要两个(当采用BPSK调制来传输数据比特流时)分支度量,而这些分支度量值可以由解码输入和另一个解码器的中间软输出计算得到。

式(4)中,前向状态度量根据编码器状态(对应于每级或时刻n)的网格表示从n=0时刻进行递归计算(由于在对数域内,采用累加)得到,这里假定的初值为,当1≤k≤2M-1时,。其中,M是编码生成多项式(1+D2+D3)的幂。类似的,式(5)中的反向状态度量从网格级n=N+1开始进行递归计算得到,同样假定的初始状态为和,其中1≤k≤2M-1。状态度量和的递归算法如下。

![]() (4)

(4)

![]() (5)

(5)

其中,b(i,m)和f(i,m)分别是与第n级的状态m相关的第n-1级和第n+1级状态值。在α,β和LLR的计算中,我们必须解一个形如ez=ex+ey的方程。其和的近似值可由ex=emax(x,y)(1+e-|x-y|)或z=max(x,y)+ln(1+e-|x-y|)= max*(x, y)计算得到。该算子被称为Log-MAP算子。修正项ln(1+e-|x-y|) 是一个非线性函数,它对MAP解码器在低信噪比下的性能增益带来最高0.5dB的提高。如果我们忽略了这个修正项,算子z=max(x,y)则被称为Max-Log-MAP算子。本文只考虑Turbo MAP解码器实现中的Max-Log-MAP算子。

TURBO解码器的实现

Turbo解码器由两个MAP解码器组成,这两个解码器由一个交织器和解交织器分隔开。由于篇幅有限,我们将不讨论Turbo解码器的完全实现而只讨论性能敏感度最高的“度量计算”部分。

1度量计算

式(1)中LLR的值由APP求得,而APP则由式(2)和式(3)计算得到。在计算APP时,我们要用到第n级所有状态下的α (前向状态度量),β(后向状态度量)和γ(分支度量)。在第n级,γ值根据已接收到的信息和第n级的外部信息计算得到,而α用第n-1级的α和第n级的γ计算得到,β则由第n+1级的β和第n级的γ计算得到。换句话说,为了计算第n级的LLR值,我们要同时利用由前n级计算出的α值和由后N-n级计算出的β值,如图1所示。

图1 第n级LLR的计算图解

2 基于窗口的算法实现

如图1所示,Turbo解码器工作于符号长度为N的序列或结构上。因此,Turbo解码器的实现就需要一个超大容量的存储器(用来存储所有N级的α、β、γ、LLR、外部信息、接收序列、缓存等等),但是可以通过加窗的方法降低对存储容量的要求。基于加窗口的方法就是将整个数据结构分成一些小的数据块或数据窗(有6K级窗口的重叠,K=M+1,是编码器的约束长度),每次只在一个窗口上执行解码操作。在 MAP 解码中,三个主要的算子是α估计,β估计和LLR估计。在计算当前窗的β和LLR的同时,计算下一个窗中的α,这样就可以平衡ALU和DAG(加载/存储)单元对带宽的需求,如图2所示。

图 2 基于窗口的Turbo解码器的高效实现

上一篇:遥控LED广告牌