随着数字信号处理理论和计算机的不断发展,现代工业生产和科学技术研究都需要借助于数字处理方法。进行数字处理的先决条件是将所研究的对象进行数字化,因此数据采集与处理技术日益得到重视。在图像处理、瞬态信号检测、软件无线电等一些领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。现在的 高速数据采集 处理卡一般采用高性能数字信号处理器( DSP )和高速总线技术的框架结构。

DSP用于完成计算量巨大的实时处理算法,高速总线技术则完成处理结果或者采样数据的快速传输。DSP主要采用TI或者ADI公司的产品,高速总线可以采用ISA、PCI、USB等总线技术。目前,使用比较广泛的是PCI总线,虽然其有很多优点,但是存在如下严重缺陷;易受机箱内环境的影响,受计算机插槽数量的地址、中断资源的限制而不可能挂接很多设备等。

USB总线由于具有安装方便、高带这、易扩展等优点,其中US

B2.0标准有着高达4800bps的传输速率,已经逐渐成为计算机接口的主流。本文介绍一个采用USB2.0接口和高性能DSP的高速数据采集处理系统,主要是为光纤通信中密集波分复用系统的波长检测与调整所设计的,也可以应用于像图像处理、雷达信号处理等相关领域。

1 高速数据采集处理系统原理及器件选用

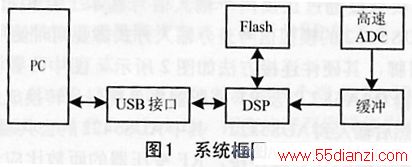

整个高速数据采集处理系统的硬件构成为:高速ADC、高速大容量数据缓冲、高性能DSP和USB2.0接口。系统的原理框图如图1所示。

高性能DSP采用TI公司的TMS320C6000系列定点DSP中的 TMS320C6203B;高速ADC采用TI公司的ADS5422,14位采样,最高采样频率为62MHz;PC机接口采用USB2.0,理论最大数据传输速率为480Mbps,器件选用Cypress公司EZ-USB FX2系列中的 CY7C68013 ;数据缓冲采用IDT公司的高速大容量FIFO器件IDT72V2113;程序存储在Flash存储器中,器件选用 SST291E010。下面逐一介绍各个器件的主要特性。

(1)TMS320C6203B

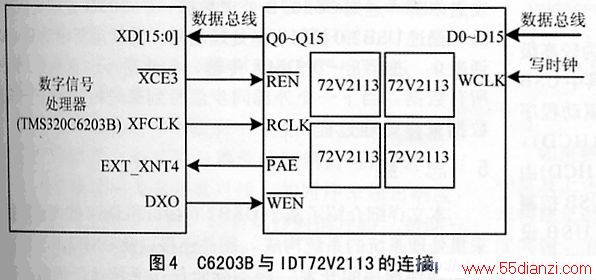

TMS320C6203B是美国TI公司高性能数字信号处理器TMS320C6000系列的一种,采用修正的哈佛总线结构,共有1套256位的程序总线、两套32位的程序总线和1套32位的DMA专用总线;内部有8个功能单元可以并行操作,工作频率最大为300MHz,最大处理能力为2400MIPS;内部集成了外围设备接口,如外部存储器接口(EMIF)、外部扩展总线(XB)、多通道缓冲串口(McBSPs)和主机接口(HPI),与外部存储器、协处理器、主机以及串行设备的连接非常方便。

(2)ADS5422

ADS5422是由美国TI公司生产的高速并行14位模数转换器,其最高采样频率达到 62MHz,采样频率为100MHz时,SNR为72dB,SFDR为85dB。模拟信号输入可以是单端输入方式或者差分输入方式,最高输入信号峰峰值为 4V,单一5V电源供电。输出数字信号完全兼容3.3V器件,并且提供输入信号满量程标志以及输出数字信号有效标志,从而方便和其它器件的连接。

(3)IDT72V2113

IDT72V2113是由美国IDT公司生产的高速大容量先进先出存储器件(FIFO)。其最高工作频率为133MHz;容量为512KB,可以通过引脚方便地将容量设置成512K×9bit或者256K×18bit两种方式; IDT72V2113可以设置标准工作模式或者FWFT(First Word Fall Through)工作模式,并提供全满、半满、全空、将满以及将空等五种标志信号;非常方便进行容量扩展。容量扩展是IDT72V2113的一大特点,扩展方式可分为字长扩展和字深扩展。通过容易扩展可以由多片IDT72V2113形式更大容量的缓冲,并且电路连接简单、可靠。

(4) CY7C68013

CY7C68013是美国Cypress公司推出的USB2.0芯片,是一个全面集成的解决方案,它占用更少的电路板空间,并缩短开发时间。CY7C68013主要结构如下:包括1个8051处理器、1个智能串行接口引擎(SIE)、1个 USB收发器、16KB片上RAM(其中包括4KB FIFO)存储器以主1个通用可编程接口(GPIF)。

点击看原图

CY7C68013独特 的架构具有如下特点:

①包括1个智能串行的接口引擎(SIE),它执行所有基本的USB功能,将嵌入的MCU解放出来以用于实现其它丰富的功能,以保证持续高速有效的数据传输;

②具有4KB的大容量FIFO用于数据缓冲,当作为从设备时,可采用 Synchronous/Asynchronous FIFO接口与主设备(如ASIC, DSP 等)连接;当作为主设备时,可通过通用可编程接口(GPIF)形式任意的控制波形来实现与其它从设备连接,能够轻易地兼容绝大多数总线标准,包括ATA、UTOPIA、EPP和PCMCIA等;

③固件软配置,可将需要在CY7C68013上运行的固件,存放在主机上,当USB设备连上主机后,下载到设备上,这样就实现了在不改动硬件的情况下很方便地修改固件;

④能够充分实现USB2.0(2000版)协议,并向下兼容USB1.1。

2 高速数据采集 处理系统的硬件连接

2.1 模拟信号输入电路

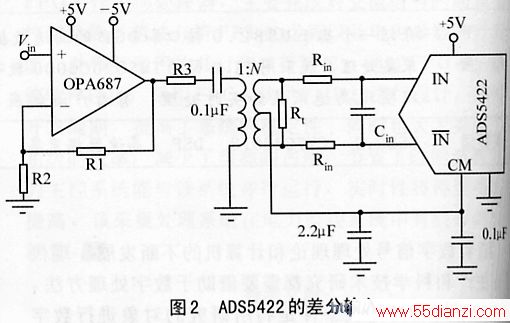

ADS5422的模拟信号输入可以采取单端输入方式或者差分输入方式。单端输入方式连接比较简单,但抗噪性能差,所以我们采取差分输入方式,以尽量减少信号噪声以及电磁的干扰,尤其是采用差分输入方式可以将所有偶次谐波通过正反反个输入信号基本上互相抵消。

ADS5422的模拟信号差分输入方式需要同时使用IN和IN引脚,其硬件连接方法如图2 所示。图中,首先使用放大器OPA687以及RF变压器将单端信号转换成差分信号,然后输入到ADS5422,其中ADS5422的公共端CM和RF变压器的公共端连接,RF变压器的匝数比应该根据信号确定。为了增强信号的稳定性,在ADS5422每个信号的输入前加上RC低通滤波电路,图2中推荐Rt为 50Ω,Rin为22Ω,Cin为10pF,这些元件也可以根据具体的信号进行调整,一般情况下电阻值在10~100Ω之间,电容值在10~200pF之间。

点击看原图

2.2 ADS5422与IDT72V2113的连接

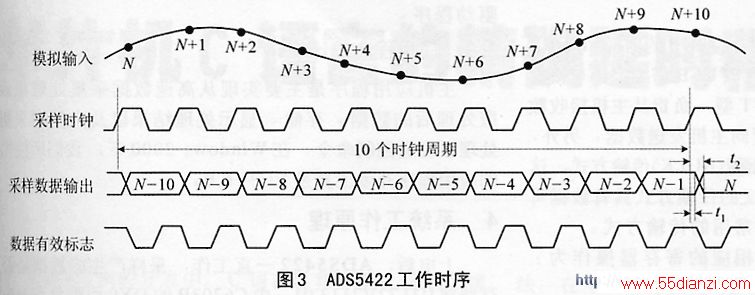

虽然ADS5422的供电电压为5V,但其输出的数字信号电平兼容3.3V电平,因此不需要电平转换芯片,只要将ADS5422的数据线与IDT72V2113的数据线相连即可。但是,ADS5422采样和存储采样数据到IDT72V3113 中,这两个操作对时序配置要求非常严格,如果两者时序关系配合得不是很好,就会发生数据存储出错或者掉数。如何简单、可靠地实现采样和存储是设计这部分电路的难点。一般的方法是,通过可编程逻辑器件(CPLD或FPGA)来实现ADC与FIFO存储器之间的时序,即由CPLD或FPGA来控制ADC采样和 FIFO存储器的写操作。但是,通过仔细查看ADS5422和IDT72V2113的工作时序图,找到了一种简单可靠的实现方法,此方法不需要CPLD或 FPGA就可以实现两者的时序配合。

www.55dianzi.com

首先分析ADS5422的工作时序图,如图3所示,其中t1为采样时钟上跳沿到输出数据无效之间的时间间隔,即数据保持时间,其大小为3ns。查看IDT72V2113的相关文档可知,对其进行写操作时,数据线的保持时间大于1ns即可满足要求。因此,ADS5422与IDT72V2113之间的时序配合可以采用以下简单的实现方法:ADS5422的采样时钟和IDT72V2113的写时钟采用同一个时钟源,这样,每一个时钟的上跳沿,ADS5422进行模数转换,同时将上个时钟周期内输出的采样数据存储到DT72V2113内部。

上一篇:从LCD电极读数的单片机接口技术