摘要:详细阐述一种采用PIC16C55 单片机 实现可控数字语音延迟器的设计方案,同时提供控制电路图及软件算法流程图。

关键词:延迟器 语音信号 PIC 单片机

延迟器在音频信号处理中有着重要而特殊的用途,是制造混响器、回声信号的重要部件,在无线通信同步控制中也起着重要作用。延迟器大致可分为BBD (Bucket Brigade Device)式延迟器和数字式延迟器两类。数字式延迟器与BBD式延迟器相比,具有延时时间范围宽,工作频带宽,动态范围大等特点;而可控式延迟器可以灵活产生多种时延,以便应用于不同的场合。本文介绍一种基于PIC系列 单片机 的可控数字语音延迟器的设计方案。

本系统采用性价比极高的PIC16C55 单片机 作为中心控制部件。PID16C55单片机是PIC系列单片机中的低档型单片机,具有20个I/O,1个定时器和1个WDT,其最短指令周期可达200ns。利用该型号单片机作为控制部件,具有控制快速、扩展方便、低功耗、性能稳定等特点,同时还可以最大限度地减少外围电路以降低成本,提高性价比。

1 系统工作原理

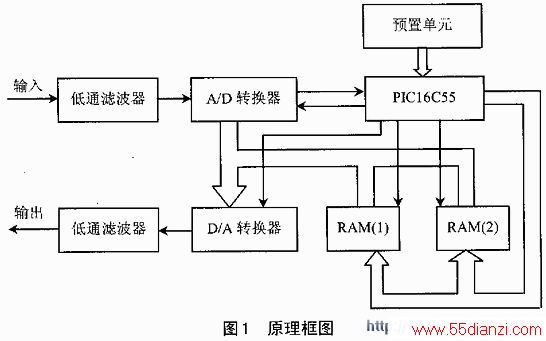

可控数字语音延迟器的原理框图如图1所示。输入的语音信号先经过低通抗混迭滤波器,滤除其中的高频成分后送入A/D转换器。经过A/D转换后,信号变成数字信号。该数字信号在PIC16C55 单片机 的控制下被写入存储器。系统中高有两组存储器,这两组存储器在单片机的控制下交替工作:在一个延迟周期内,一组存储器专门用于存储本周期内采集的数据,而另一组存储器专门用于把上一个周期所采集的数据按顺序送到数据总线,经过D/A转换器和低通滤波器后恢复出原始信号。在下一个延迟周期,两组存储器交换工作状态,以后按此不断循环。可见,延迟的时间取决于A/D转换器前后两次启动的时间间隔和存储区的大小。在本系统中,利用PIC16C55中的定时器定时产生A/D转换器的启动信号,定时器的定时时间为10μs,所以,最小延迟时间为10μs。而存储区的大小设为256,所以,最大延迟时间为10μs×256=2560μs=2.56ms。系统中的预置单元用来设置延迟单元数,进而得到所需的延迟时间。

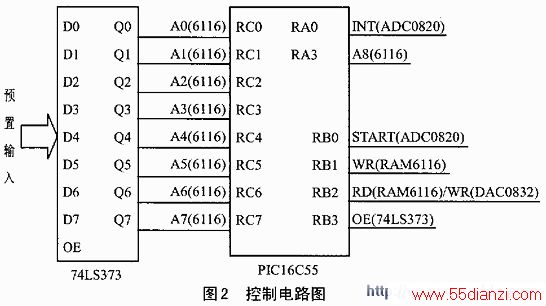

系统中PIC16C55 单片机 是中心控制部件。它的主要任务有:定时控制A/D转换器进行转换;控制RAM(1)、RAM(2)的读写;控制D/A转换器的转换;产生RAM(1)、RAM(2)的地信息;控制RAM(1)、RAM(2)的交替;接受预置输入。控制电路如图2所示。

PIC16C55 除了控制转换及读写外,还要产生RAM的地址信息及接收预置输入。在本系统中,由PIC16C55的RC口产生地址信息,同时也能接收预置输入。系统中利用74LS373作为预置输入的缓存,而74LS373的OE端由RB3控制。当RC口作为地址发生器时,RB3=OE=1,即74LS373的输出不允许,其输出端为高阻态;当RC口接收预置输入时,RB3=OE=0,即74LS373的输出允许,其输出端为预置输入。系统中两组存储区的选择由RA3控制:当RA3=A8=0时,选择的存储区为00H~FFH单元;当RA3=A8=1时,选择的存储区为100H~1FFH单元。

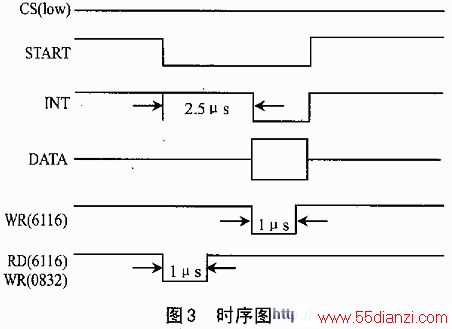

PIC16C55 除了控制转换及读写外,还要产生RAM的地址信息及接收预置输入。在本系统中,由PIC16C55的RC口产生地址信息,同时也能接收预置输入。系统中利用74LS373作为预置输入的缓存,而74LS373的OE端由RB3控制。当RC口作为地址发生器时,RB3=OE=1,即74LS373的输出不允许,其输出端为高阻态;当RC口接收预置输入时,RB3=OE=0,即74LS373的输出允许,其输出端为预置输入。系统中两组存储区的选择由RA3控制:当RA3=A8=0时,选择的存储区为00H~FFH单元;当RA3=A8=1时,选择的存储区为100H~1FFH单元。系统正常工作时的时序如图3所示。当START变为低电平时,ADC0820开始转换,转换时间约为2.5μs。在ADC0820转换期间,读存储区开始读操作,同时DAC0832开始转换,存储区的读操作时间设为1μs。当ADC0820转换结束后,INT变为低电平,同时写存储区进行写操作,延时1μs后,START设为高电平。至此,一次的转换和一次的读写操作已经操作已经完成。从此刻到下一次A/D转换开始的时间内,主要完成的操作有:存储地址的改变、两组存储区的交替及预置值的读入。

程序流程如图4所示。

结束语

笔者根据本文的设计方案制作了实际电路,效果良好。在实际应用中,读者可根据实际情况灵活改变最小延迟时间和最大延迟单元数。通过改变PIC16C55中定时器的定时时间即可改变最小迟时间;通过改变存储区的大小即可改变最大延迟单元数,进而改变最大延迟时间。

本文关键字:语音 PIC单片机,单片机-工控设备 - PIC单片机