“一个蝴蝶可以刮起一阵风,一个士兵可以开始一场战争”,那么一项伟大的发明呢?

1947年12月,美国贝尔实验室的肖克莱、巴丁和布拉顿组成的研究小组,研制出一种点接触型的锗晶体管。于是乎,大名鼎鼎的、影响人类文明进程的晶体管就此诞生。1956年,这三人因发明晶体管同时荣获诺贝尔物理学奖。

在晶体管诞生60多年后的今天,其体积几乎缩小到了极限:贝尔实验室1947年制造的第一个晶体管是手工打造的,而现在一个针头的空间就能塞进去 6000多万个32nm晶体管(针头直径约1.5毫米);如果百米飞人博尔特的步幅是32nm,那么完成一百米赛程需要跑31.25亿步;32nm晶体管的栅极长度约为30nm,英文句点符号“.”的面积大约有0.1平方毫米,可以放进去400多万个32nm晶体管;Intel 32nm技术的栅极高度是0.9nm,而报纸的平均厚度为0.1毫米,也就是说111111个栅极堆叠起来才有一张报纸厚。

所有数字都揭示着晶体管已经“小”到令人叹为观止。但是凡事都有个极限,无限接近物质的极限意味着晶体管已经步入老年了吗?

晶体管的前世今生晶体管被认为是现代历史中最伟大的发明之一,在重要性方面可以与印刷术、汽车和电话等发明相提并论。晶体管的本名是半导体三极管,是内部含有两个PN结,外部通常为三个引出电极的半导体器件。它对电信号有放大和开关等作用,应用十分广泛。晶体管出现后,人们就能用一个小巧的、消耗功率低的电子器件,来代替体积大、功率消耗大的电子管了。

晶体管的发明为后来集成电路的问世吹响了冲锋号。除了能够很方便的储存信息、发送信号,晶体管还具有当初人们不曾料想的特性:它可持续缩小体积,这使得晶体管与电子产品可以稳定地降价,且功能变得越来越好。这一理论最终成就了摩尔定律。

2006年2月英特尔正式推出45nm晶体管(图1)。与65nm芯片相比,其密度提高2倍,达10亿个晶体管,开关速度提高20%,功耗降低30%。这种45nm工艺采用了Cu互连、低k介质,应变硅和193nmArF光刻。

2010-9-20 12:32:43 上传下载附件 (24.02 KB)

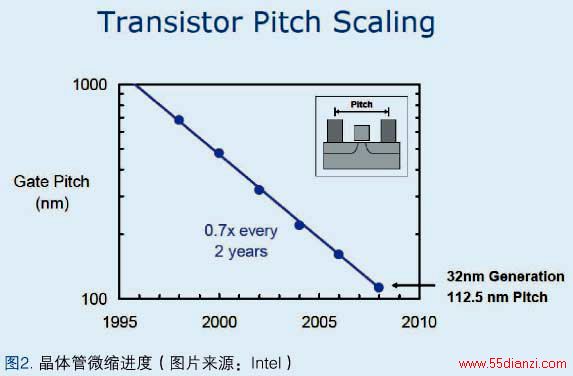

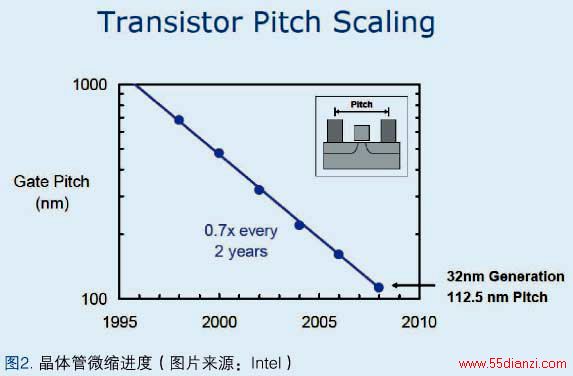

2010-9-20 12:32:43 上传下载附件 (24.02 KB) 32nm晶体管则采用第二代高k金属珊技术,即栅的长度为30nm左右,等价的栅极氧化物厚度仅为0.9nm,同时整体性能将有超过22%的提升。32nm SRAM 测试芯片最早出现在2007年9月,芯片尺寸可以从45nm的0.346μm2减小到0.171μm2。回顾Intel的晶体管技术发展历程,Intel 每两年即可将晶体管的尺寸缩小30~50%(图2)。

2010-9-20 12:32:43 上传下载附件 (26.18 KB)

2010-9-20 12:32:43 上传下载附件 (26.18 KB) 摩尔定律是一个残酷无情的 “监工”,就在最新技术刚刚投入生产,人们认为可以暂时停下脚步好好休息一下时,往往会愕然发现,下一代技术在两年后就要按时推出,再过两年又一代新技术……

IBM院士Stuart S.P. Parkin博士介绍说,有摩尔定律的指引,新器件的出现是必然的,它的进步速度在很大程度上取决于相关材料、设备的进展,当然也和市场紧密相连。在晶体管的技术路线图上,22nm节点之后的等比例缩小很可能需要在SOI或体硅晶圆上采用全耗尽CMOS结构。也很可能会采用TSV 3-D互连和SiC应力层。

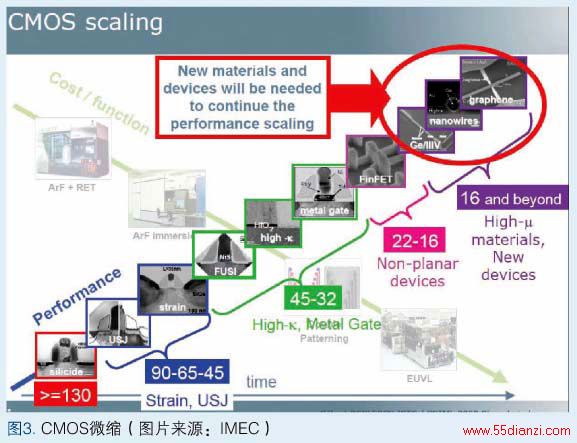

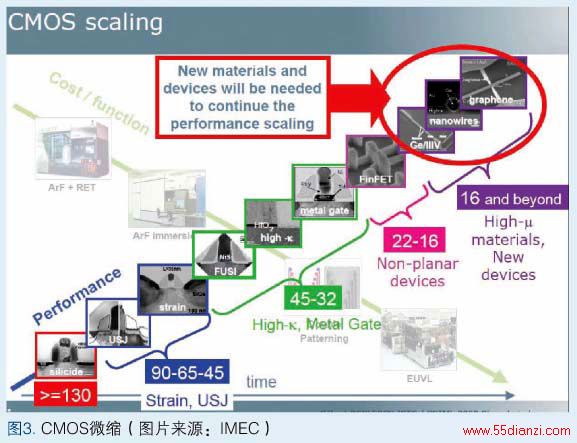

向新器件结构的转换已经启动(图3),在15 nm技术路线图上,IBM和英特尔已经确认了全耗尽CMOS结构,而一些其它的垂直晶体管结构也得到了极大重视。部分耗尽或传统的体硅晶体管变得愈加困难,为了获得所需的短沟性能,需要全耗尽器件架构――像finFET这样的垂直器件或平面SOI――才可以完成对沟道的控制。

2010-9-20 12:32:44 上传下载附件 (55.54 KB)

2010-9-20 12:32:44 上传下载附件 (55.54 KB) 尽管普遍的观点是全耗尽结构会出现在15nm节点,但IBM已经考虑22nm技术节点时,在其旗舰MPU工艺技术中采用全耗尽工艺。英特尔在 22nm还将继续采用体硅技术。英特尔将于2011年底推出采用22nm工艺的MPU。去年九月英特尔发布了带有SRAM阵列和周边逻辑电路的22nm测试芯片,其中每个存储器阵列为364Mb,芯片共有290亿个晶体管。该芯片采用了第三代后栅极高k/金属栅工艺,也就是在栅极工艺的最后沉积栅介电层和金属。

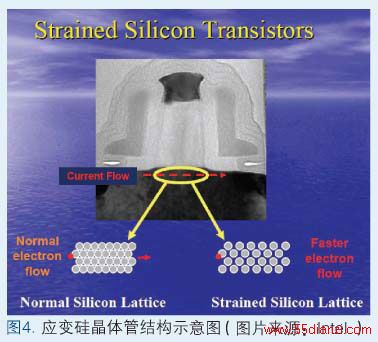

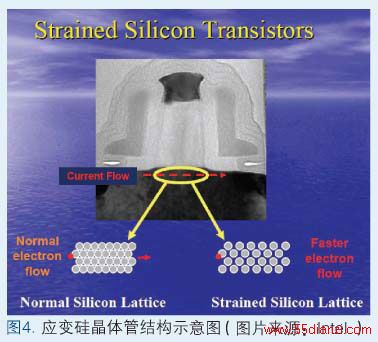

应变硅如何“应变”?半导体工业缩小芯片的主要动机是:增加每一片晶圆上的芯片数目,从而降低成本;缩短载流子扩散路径,从而提高芯片处理速度。但是,芯片小型化使工艺技术面临着新的问题:散热和量子隧道效应的处理。一个新的思路就是寻找新的电子材料,基于硅材料的应变硅技术由此诞生。

在2009年北京微电子论坛先进半导体工艺研讨会上,中芯国际的技术处长吴汉明博士为大家展示了晶体管未来的走向,应变硅技术是杀手锏之一。应变硅是满足65nm以下工艺要求的一种高端硅基新材料。应变硅由在SiGe等原子距离较大的衬底上外延生长Si而成。该材料的制作原理之一是在锗硅上外延硅,由于硅原子在锗原子之间力的作用下发生了应变,扩张了原子间距,因而这种材料被称为“应变硅”。当硅晶格受到应力产生应变,可将传输载子的有效质量缩小,迁移率及饱和速度均增加。因此在同样组件尺寸下,若使用应变硅技术作为载子的传输通道,因其电子与空穴的载子迁移率增加,可达到增加组件速度与驱动电流的目标。

形成应变的方式很多,可藉由制程工艺、材料上自然晶格常数的差异或是组件封装等等方式来达成。应变硅则可通过如下三种方法获得:(1)工艺诱导法,通过晶体管周围薄膜和结构之间的应力形成;(2)在器件通道下方嵌入Si-Ge层;(3)对整片晶圆进行处理。英特尔推出一种包含全硅化(FUSI)镍电极的45nm节点技术,并将由FUSI生成的金属与单轴应变硅沟道相结合,硅化电极提高了电荷密度,应变硅增强了载流子迁移率,从而使其性能比传统的氮氧化硅-多晶硅栅电极提高20%,改进驱动电流20%。东芝推出一种合并两种应变硅形成的45nm节点工艺,它把双应力衬底和位于漏/源极区域的淀积Si- Ge相结合,避免将高k介电材料引入栅氧化物,仍继续采用氮氧化物(SiON)。

总体来说,应变硅技术对硅进行了拉伸,从而加速了电子在芯片内的流动,不用进行小型化就可以提高性能和降低功耗。Stuart S.P. Parkin博士对应变硅的前景表示乐观,认为如果与绝缘硅技术一起使用,应变硅技术可以更大程度地提高性能并降低功耗。其未来挑战在于如何了解并优化各种不同来源应力之间的相互作用。

2010-9-20 12:32:44 上传下载附件 (30.4 KB) 新型晶体管FinFET:万丈高楼平地起

2010-9-20 12:32:44 上传下载附件 (30.4 KB) 新型晶体管FinFET:万丈高楼平地起“万丈高楼平地起”,没错,晶体管也要“拔地而起”了。通过简单地缩小垂直尺寸和水平尺寸来开发新一代晶体管技术的时代早已过时。Intel资深 fellow Yan Borodovsky博士说:“摩尔定律毫无疑问仍将继续,但找到兼顾性能与成本的最佳方案乃首要任务,取代 “传统”形式的技术升级,现在必须开发新材料和新结构,提供更小的尺寸,满足人们对高密度、高性能和低能耗的要求。”

为了提高45nm晶体管电流密度、减小短沟道效应和改善栅极控制,业界提出了多种新型晶体管结构,如三栅极结构、FinFET(鳍式场效晶体管,Fin Field Effect Transistor)、Omega-FET和多栅极FET等。

平面器件不可能被无限微缩下去。如果采用FinFET,就好像打开了一扇新的门,可以通过集成垂直器件而提升晶体管密度。FinFET确实有进一步提高晶体管密度的潜力,IBM在2009年将其用于FinFET研究的晶圆数目增加了一倍。

FinFET是一种新的CMOS晶体管,被誉为22nm的革命性器件之一(图5)。它的栅极长度已可小于25nm,未来预期可以进一步缩小至 9nm,约是人类头发宽度的1万分之1。FinFET源自于目前传统标准的晶体管―场效晶体管的一项创新设计。Stuart S.P. Parkin博士说,在传统晶体管结构中,控制电流通过的栅极,只能在栅极的一侧控制电路的接通与断开,属于平面的架构。在FinFET的架构中,栅极成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计大幅改善电路控制并减少漏电流,还能大幅缩短晶体管的闸长(图6)。

[1] [2] 下一页

本文关键字:晶体管 电工文摘,电工技术 - 电工文摘

2010-9-20 12:32:43 上传下载附件 (24.02 KB)

2010-9-20 12:32:43 上传下载附件 (24.02 KB)  2010-9-20 12:32:43 上传下载附件 (26.18 KB)

2010-9-20 12:32:43 上传下载附件 (26.18 KB)  2010-9-20 12:32:44 上传下载附件 (55.54 KB)

2010-9-20 12:32:44 上传下载附件 (55.54 KB)  2010-9-20 12:32:44 上传下载附件 (30.4 KB)

2010-9-20 12:32:44 上传下载附件 (30.4 KB)