2010-9-20 12:32:44 上传下载附件 (25.76 KB)

2010-9-20 12:32:44 上传下载附件 (25.76 KB)  2010-9-20 12:32:45 上传下载附件 (56.78 KB)

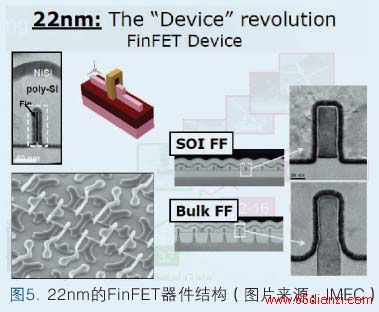

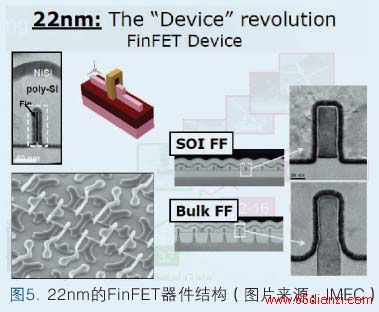

2010-9-20 12:32:45 上传下载附件 (56.78 KB) 习惯是一种可怕的东西,往往会阻碍创新,“平面结构”由于保持了人们习惯的设计风格因而备受欢迎。但采用了FinFET,则必须把器件加起来使用。设计时不存在随意的宽度,因此只能将其量化并增加指型沟道的数目。FinFET工艺非常困难是业界人士的共识。

对于光刻来说,要能够克服侧壁图形转移的问题;对于刻蚀来说,栅极刻蚀则是另一个挑战。在指型结构附近栅极会卷曲,使得栅极轮廓的表征非常困难。对那些可接受的晶体管性能来说,栅极需要尽量直。在平面结构中,栅极在一个平面上,但在FinFET中,栅极在整个晶圆的表面与沟道高低交错。这带来一些根本性的问题,需要找到集成所有工艺完成整个器件的方法。由于垂直结构带来的光刻和刻蚀挑战,大多数公司都对FinFET非常谨慎,从某种程度上来讲,通过外延抬升源极/漏极的结构本质上已经是一种垂直结构了。

在2009年的IEDM上,采用FinFET技术实现0.06μm2或者0.039μm2单元面积的超微细SRAM亮相。但是,这些产品都利用了电子束直描技术,实用化方面还存在问题。美国IBM、美国GLOBALFOUNDRIES、东芝及NEC电子(现为瑞萨电子)组成的小组近期发布了以现有ArF光刻技术实现的0.063μm2超微细SRAM研究成果。通过采用Sidewall Image Transfe技术,实现了40nm的Fin间距,解决了基于FinFET的SRAM的另一课题――因使用多个Fin而导致面积增大的问题。同时,还实现了80nm这一全球最小的栅极间距。作为实现超微细SRAM的技术,这一成果给人FinFET更为出色的强烈印象。FinFET大展拳脚的时间点似乎更加明朗化。

SOI:CPU煮熟鸡蛋将成为历史CPU热到可以煮熟鸡蛋的故事已成经典,它说的正是芯片功耗过高的问题。曾有人预言,高功耗将导致摩尔定律提前终结。这并非危言耸听。高功耗产生高温度,提高了封装成本,也产生了许多新的故障,加大了测试复杂度,提高了测试成本。高的芯片功耗产生很多负面影响,而为了保证摩尔定律,就要采用低功耗设计,这又反过来加大了设计复杂度。凡此种种都对摩尔定律产生了终结效应。

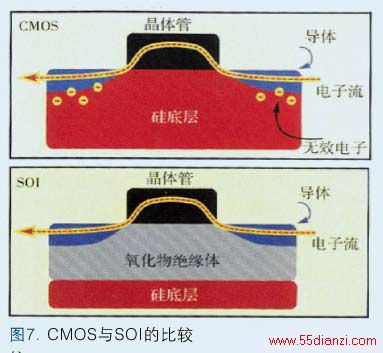

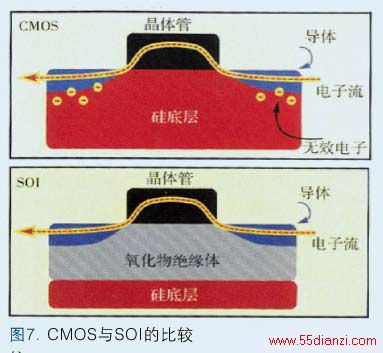

Stuart S.P. Parkin博士说,绝缘硅(SOI,Silicon-On-Insulator)的出现主要是解决芯片的功耗问题,这是22nm节点晶体管的希望,当然也是挑战。该技术利用一层SiO2绝缘薄膜,将各个晶体管与最底下的硅晶圆分开,而在常规的CMOS中,晶体管是直接与硅晶圆接触的(图7)。SiO2薄膜层能有效的使电子从一个晶体管的门电路流到另一个晶体管的门电路,不会让多余的电子渗漏到晶圆上。由于不会有电子渗漏而浪费电能,因此功耗更小。

2010-9-20 12:32:45 上传下载附件 (25.8 KB)

2010-9-20 12:32:45 上传下载附件 (25.8 KB) 通过在绝缘体上形成半导体薄膜,SOI材料具有了体硅所无法比拟的优点:可以实现集成电路中元器件的介质隔离,彻底消除了体硅CMOS电路中的寄生闩锁效应;采用这种材料制成的集成电路还具有寄生电容小、集成密度高、速度快、工艺简单、短沟道效应小及特别适用于低压低功耗电路等优势。

据IBM公司的数据显示,同类SOI芯片与CMOS芯片相比,SOI芯片的速度可以快20%~30%,而能耗为CMOS芯片能耗的一半或三成。采用SOI技术的45nm PMOS晶体管驱动电流增加30%。

在22nm节点,SOI晶圆上关键硅层的厚度是6.3nm,而15nm则更薄,约5nm。硅层是如此之薄,如果破坏了顶层的硅,那么根本没有修复的余地。为了避免材料损伤,采用了原位掺杂而非注入工艺,这是因为原位掺杂是一项无损伤的工艺。

目前比较广泛使用且比较有发展前途的SOI的材料主要有注氧隔离的SIMOX(Seperation by Implanted Oxygen)材料、硅片键合和反面腐蚀的BESOI(Bonding-Etchback SOI)材料和将键合与注入相结合的Smart Cut SOI材料。在这三种材料中,SIMOX适合于制作薄膜全耗尽超大规模集成电路,BESOI材料适合于制作部分耗尽集成电路,而Smart Cut材料则是非常有发展前景的SOI材料,它很有可能成为今后SOI材料的主流。

其实,晶体管一路走来的历史,就是技术的不断新陈代谢和市场诉求相辅相成的过程。当整个产业链发展进入良性循环时,一切的发展进步都将会是顺理成章的,好在这样的趋势正在发生。

上一页 [1] [2]

本文关键字:晶体管 电工文摘,电工技术 - 电工文摘

2010-9-20 12:32:44 上传下载附件 (25.76 KB)

2010-9-20 12:32:44 上传下载附件 (25.76 KB)  2010-9-20 12:32:45 上传下载附件 (56.78 KB)

2010-9-20 12:32:45 上传下载附件 (56.78 KB)  2010-9-20 12:32:45 上传下载附件 (25.8 KB)

2010-9-20 12:32:45 上传下载附件 (25.8 KB)