1��������

�����ֳ��ɱ����������FPGA�����ڼ�߿ɱ���������ֳ��ɱ�̵�����ԣ��Լ��������������ɶȸߵ��ŵ㣬������ϵͳ����б��㷺ʹ�á�FPGA���Ź������ڲ��������кͷḻ��������Դ���ر��ʺ���ϸ���Ⱥ߲��жȽṹ�ص�������źŴ���������FIR��FFT�ȡ�������ϸ����������FPGAʵ��FIR�˲�������ƹ��̣����Ҷ�����еĹؼ����������ֲ�ʽ�㷨�ͻ���RAM����λ�Ĵ�������������ϸ��������������Ѿ�ͨ����FPGA��֤��������ͬ�������ȣ���������Ƶĵ�·�����ٶȿ����ռ�õ����С��

2��FIR�ͷֲ�ʽ�㷨

2��1��FIR�Ļ�������

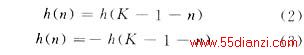

FIR�˲�����ѧ����ʽΪ��

![]()

�����ɴ˿�����FIR�˲����Ļ����ṹ��һ���ֽڵ���ʱ�ߣ���ÿһ�ڵ������Ȩ�ۼӣ��õ��˲��������������FIR�˲������ڷ�����ֻ������������������֮һ�����ܹ���������λFIR�˲�����

ʽ��2����Ϊ��һ��������λ�ķ���������ʽ��3����Ϊ�ڶ���������λ�ķ����������ɴ˿�д��������λFIR�˲�������ѧ����ʽ��

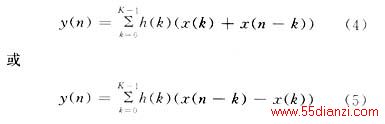

![]()

���У�hk��h��k����xk��n����x��n��k����KΪ�˲����ij��ȡ�

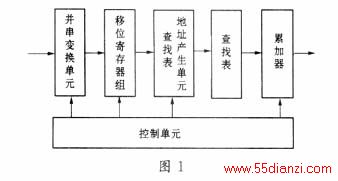

����Ϊ��ʹ�ó˷�֮������ݿ��Ȳ�����չ�����Ȱ�����Դ���ݸ�ʽ�涨Ϊ������2�IJ�����ʽ����

![]()

���У�xkb��n��Ϊ����������ȡֵΪ0��1��xk0��n��Ϊ����λ��xk0��n��Ϊ1��ʾ����Ϊ����Ϊ0��ʾ����Ϊ��������7��ʽ���루6��ʽ�ɵ�

�����ɴ˿������������н��е������������һ������λ�������˲�����ͷϵ��h0��hk��ÿһλ���������㲢��͡���ָ��������˵������ͽ����λȨ����������2��b��������bλ���Դ˿���ͨ��Ӳ����ʵ�֣���ռ������Դ����������ͨ���������ұ���ʵ�ַ������еIJ��������ұ����������������ͬһλ����Ѱַ��

����������ʽ��6������ʾ�ķ��̾Ϳ����ɼӷ��������Ͷ����Ƴ�����ʵ���ˡ�

3��ϵͳ�����ʵ��

3��1��ϵͳ�������

����������һ��10��������λFIR�˲������������ݺͳ�ͷϵ����λ����Ϊ16���أ�Ϊ��˵����·����ƹ��̡�

�������ݣ�ȫ���У��ֲ�ʽ�㷨��ԭ����������λFIR�˲����ɷ�Ϊ�����任��Ԫ����λ�Ĵ����顢���ұ���ַ������Ԫ�����ұ����ۼ����Լ����Ƶ�Ԫ����ṹ��ͼ��ͼ1��ʾ��

����ϵͳ�����������£�����������������Ⱦ��������任������չһλ������������͵���λ�Ĵ������У�����λ�Ĵ������У�ÿ����λ�Ĵ���������˿ڶ�Ҫ����һ���ķ�ʽ��ÿ�����˿ڽ�����ӻ�������Դ˲��������ұ��ĵ�ַ�����Ӳ��ұ��ж�����Ӧ�����ݣ��͵��ۼ����н���������λ��ӣ��ۼӵ�һ�����������ȷ������������ǴӼ�������˿�

���룬��ô�������������پ��������任����ֱ�ӽ�����λ�Ĵ棬����Ĺ������̺�����һ�¡�

3��2�������任��Ԫ

���������任��Ԫ����Ҫ���ܾ��ǽ�������������ݰ���һ����˳�������������ʽ��4���ͣ�5�����Կ�������������x��k����x��n��k��Ҫ����Ԥ��ӻ�Ԥ�����Ϊ�˷�ֹ��������������������Ҫ������չ������������Ϊ�з��������������λǰ��չһλ����λ������������Ϊ���������������λǰ��չһλ0��

3��3����λ�Ĵ�����

������λ�Ĵ�����Ĺ����Ƕ����ݽ�����λ�Ĵ档��ʵ��ʱ������XC4000ϵ��оƬ���ں�RAM���ص㣬���û���RAM����λ�Ĵ�������Ч�ؼ�С���������RAM����λ�Ĵ������ǰ����ݴ洢��RAM�У�ͨ���Զ���д�����ʵ��IJ�����ʹд��ȥ�����ݾ���һ����ʱ�����ڲ���������Ӷ�ʵ����λ�Ĵ�Ĺ��ܡ�оƬ���ں�RAM������ʹ��һ��CLB�д洢�ߴ�64���ص����ݣ�������һ��CLB�Ĵ�������ֻ�ܴ洢2���ص����ݣ��������ʹ����������ݴ洢��ռ�õ���Դ�������ԣ���XC4000ϵ��оƬ�У�һ��16λ����λ�Ĵ�����Ҫռ��7��CLB��������RAM��16��1������λ�Ĵ���ֻ��ռ��1��CLB��

�������û���RAM����λ�Ĵ�������Ҫ�������ڿ���RAM�Ķ���ַ����д�����źţ���Щ���ɿ��Ƶ�Ԫ����������һ������ΪN�Ļ���RAM����λ�Ĵ���������ʹ����д���ݲ����ȶ����ݲ�����ʱһ��ʱ�����ڣ�����д�������ݣ�����N��ʱ�����ڲ���������Ӷ������λ�Ĵ�Ĺ��ܡ�

����Ϊ��ʵ���˲��������Ĺ��ܣ���Ҫ����һ������˿ڡ�����������˿ڣ���Ҫ����һ������˿ڡ�����������˿ڣ������������˲������ܹ���������ʮ����λ�Ĵ������ܶԴ��������ݶ˿���������ݽ�����λ�Ĵ棬���ܶԴӼ�������˿���������ݽ�����λ�Ĵ档����ʵ��ʱ������ʮ����λ�Ĵ����У���һ��ֻ��Լ�������˿ڵ����ݽ�����λ�Ĵ棬������Ϊ�����任��Ԫ�Ѿ��൱��һ����λ�Ĵ��ˣ��ڵڶ���������˾���Ҫ�Բ����任��Ԫ����˿ڵ����ݺ͵�һ����λ�Ĵ���������˿ڵ���������ѡ�����Ƕ��ĸ��˿ڵ�������λ�Ĵ档���һ����λ�Ĵ����������������Ϊ��������˿ڡ�

3��4�����ұ���ַ������Ԫ

�������ұ���ַ������Ԫ�Dz������ұ��ĵ�ַ���������������λ�ļӷ������������鹹�ɵġ����˲�����ϵ�������ԳƵģ�ʹ�üӷ��������˲�����ϵ���Ǹ��ԳƵģ�ʹ�ü�������

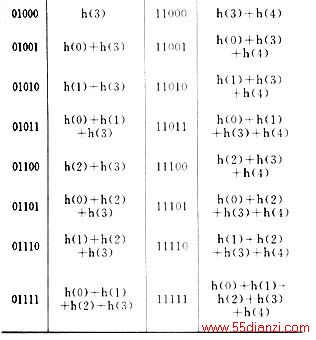

3��5�����ұ�

�������ұ��Ĺ��ܾ��Ǵ洢��ͷϵ������ϣ����Ҹ�����ַ�ܶ�����Ӧ�����ݡ����ұ�����������˲����Ľ����������ģ�����N�����˲����Ľ���������������λ�˲�������ϵ���ǶԳƵģ���ô�����ϵ���ĸ���ΪN��2��������ұ�����Ⱦ͵���2��N��2�������ڷǶԳ��˲����������ϵ���ĸ���ΪN��������ұ�����Ⱦ͵���2N������ƽ����ϳ���FIR�˲���ʱ�����ǿ��Խ���IJ��ұ�����Ϊ����С�IJ��ұ���������ռ�õ�FPGA��Դ��XILINX��˾��XC4000ϵ��FPGA��һ��CLB����ʵ��32��1��С��RAM�����磬����һ��16�ķǶԳ�FIR�˲�����ϵ������Ϊ8���أ����������л��֣����ұ�����Ⱦ�Ϊ216����Ҫռ��16384��CLB�������仮��Ϊ����Ѱַλ����Ϊ8�IJ��ұ���ÿһ����ұ�����Ⱦ�Ϊ28����ô������ұ���Ҫռ��128��CLB�������仮��Ϊ�Ŀ�Ѱַλ����Ϊ4�IJ��ұ���ÿһ����ұ�����Ⱦ�Ϊ24����ô�Ŀ���ұ���Ҫռ��16��CLB���ɴ˿��������ұ��Ļ���Ҳ�Ǽ�С�����һ���ؼ�������

�������ұ�������ROM��ʵ�֡�����10��������λFIR�˲�����˵������ϵ��Ϊ5������ROM����Ⱦ�Ϊ32����1ʾ������5������ϵ���������ROM�е�λ�á�

3��6���ۼ���

�����ۼ����Ĺ��ܾ���ͨ���м����ݵ���λ���ʵ����������ˣ��ڸõ�Ԫ��ҲҪ���з�������������ڸ��ۼ���ʵ�ֵ��൱�ڳ˷�������λ��ӣ�����ÿ�ζ�Ҫ����ӽ������һλ���ٺ���һ�ε�����������ӡ�����������������������ҳ�ͷϵ�������Գƣ���ֱ���ӵ�17�Σ������������Ϊ�з���������ͷϵ��Ϊ���Գ�Ҳ��Ϊ���Գƣ���������������Ϊ�������ҳ�ͷϵ���Ǹ��Գƣ�����ӽ���16�Σ����һ�ν��е���������㡣��λ��Ӽ��ɿ��Ƶ�Ԫ�������ź������ơ�

���Ĺؼ��֣��˲��� �繤��ժ���繤���� - �繤��ժ