3.7 控制单元

控制单元的主要功能是:对并串变换单元进行控制;产生移位寄存器组单元中的RAM的读地址以及读写操作控制;产生查找表地址产生单元中加法器或减法器的清零信号;并对累加单元进行控制。这些功能主要由计数器来实现。

4 FPGA验证

本系统的FPGA采用XILINX公司的XC4000系列芯片,各个模块用VHDL语言描述,用开发软件Synplify Pro 6.2.4编译及综合,用开发软件Xilinx Foundation Series ISE3.1i做前仿和后仿以及布局布线。

本文设计的10阶可级联线性相位FIR滤波器,其输入输出管脚情况如表2所示。

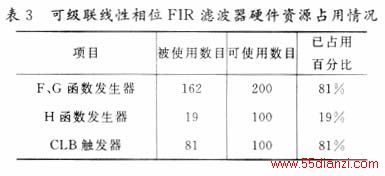

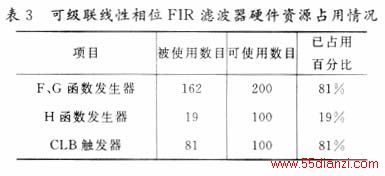

利用XC4000EPG120-1芯片进行布局布线,测试报告表明,该滤波器处理数据的时钟频率是64.8MHz,采样速率是4.05MHz。其硬件资源占用情况如表3所示。

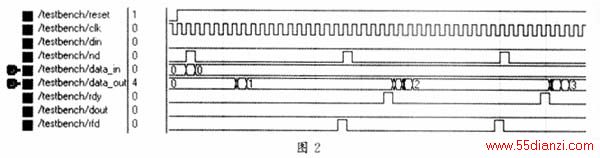

检测所设计的电路是否能正确而连续地工作,可以采用最简单的测试方法:输入一个脉冲,若输出是按顺序输出抽头系数的值,可以说电路是正常工作的。经过布局布线后,其时序仿真如图2所示。

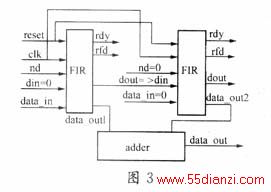

5 FIR的级联

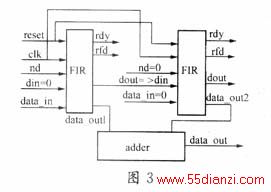

本文所设计的滤波器可以级联成更长的滤波器,用n个10阶的FIR滤波器和加法器可以组成

一个n×10阶的滤波器。通过查找表内容的设定,级联后的滤波器可以是对称的也可以是非对称的。如图3所示,用两个10阶的FIR滤波器和一个加法器可以级联成一个20阶的滤波器。

采用分布式算法,级联后的滤波器不会因为长度的增加而性能明显下降,利用XC4005EPC84-1芯片实现两级级联的滤波器时,处理数据的时钟频率为64.5MHz,所占用的CLB为156个。

6 结束语

本设计在采用分布式算法的基础上,利用基于RAM的移位寄存器,节省了大量的FPGA资源。通过阶数以及查找表中抽头系数的设定,低通、高通、带通和带阻滤波器都可以实现。

设计的电路已通过FPGA验证,证明工作正常,性能良好。

参考文献

1 丁玉美,高西全,彭学愚.数字信号处理.西安:西安电子科技大学出版社,1998

2 蒋亚坚,张庆雷.分布式运算单元的原理及实现方法.电子应用技术,2001(2)

上一页 [1] [2]

本文关键字:滤波器 电工文摘,电工技术 - 电工文摘