˫��-CMOS���ɵ�·(BiCMOS)��˫�����ŵ�·�ͻ�������-��������뵼�壨CMOS���ŵ�·���ɵļ��ɵ�·���ص��ǽ�˫����Bipolar�����պ�CMOS���ռ��ݣ���ͬһоƬ����һ���ĵ�·��ʽ��˫���͵�·��CMOS��·������һ�𣬼��и��ܶ� �����ĺ��ٴ������������ص㡣

������BiCMOS��·��20����80����������ʵ�֣���ҪӦ���ڸ��پ�̬�洢���������������Լ������������ֵ�·�У����������������������ģ������ϵ�·������ϵͳ���ɡ�����Ԥ�ԣ�BiCMOS���ɵ�·�Ǽ�CMOS���ɵ�·��ʽ֮������ʵ����һ�����ټ��ɵ�·��ʽ��

����������BiCMOS������������

1����CMOS������BiCMOS����

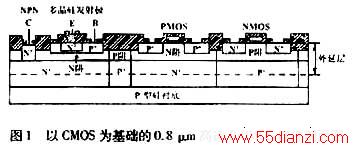

BiCMOS�����ǽ�����˫�����ֹ��պ��ʵ��ں���һ��ļ�������������Ǽ���е�ز�����һ�𣬺ܶ�տ���һ������跨�����һ������ĿǰBiCMOS������Ҫ�����֣�һ����CMOSΪ������BiCMOS���գ����ֹ��նԱ�֤CMOS���������ܽ�Ϊ������������˫������Ϊ������BiCMOS���գ����ֹ��ձȽ�����BJT���������ܡ�ͼ1����CMOSΪ������0.8��m BiCMOS��������������ͼ��

BiCMOS��C����ֻʹ������˫���Ծ��������������һ�������������BiCMOS��E������Ҫ����ECL����Ϊ������CMOS�������Ϊ���ʹ洢���������������͵�BiCMOS������Ҫ��˫���Ծ���ܺ�MOSFET�����������뵼�峡ЧӦ����ܣ�������ͬһоƬ���������ո��ӣ�������ͬ�ָ��ӳ����CMOS��������Ҫ�ߣ����ijɹ����ȡ����CMOS��GaAs�������Ӧ������ȡ�óɹ��ij̶ȡ�BiCMOS��E���ܲ���GaAs�봿ECL����������ڸߵ�Ӧ�ó������ܲ�����GaAs�봿ECL��⡣��һ���棬BiCMOS�ļ۸��ֲ���CMOS���ˣ���ˣ�BiCMOS��C������ȡ�ڼ۸��Ͻӽ���CMOS��������������Ҫ�ܸ���GaAs������

��ͼ1�ɼ���������˫��CMOS����Ϊ��������N����������N+���ͼ��缫�Ӵ���N+ע�루ͼ�����BJT�����Լ���BJT�����ļ��缫����������ֵ�����ͱ���ѹ������P+������N+����ע��������������������ȡ�ྦྷ�������ʽ����MOS������դ��������ʽһ�£������ྦྷ��BJT������������ָ���BiCMOS���칤��ԭ���ϲ���Ҫ������������Ҫ����

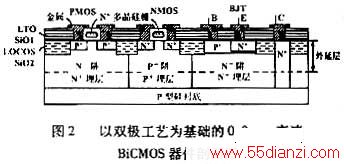

2����˫������Ϊ������BiCMOS����

Ŀǰ�ڹ��⣬�Ƚ���˫������һ���������������ͱ�����BiCMOS���ա���˫������Ϊ������BiCMOS���ռ�Ϊһ�������ֹ��յ�BiCMOS�ȹ�ȫ��CMOS������ʹ���봿CMOS�����е�����������ܺ���ѷɫ��ͬʱ�ּ����BJT������ʹ�����µĴ�˫�������е������������¡�

���ֹ�������˫��CMOS�����м��Ͼ�����Ƶ�4�Ű�ͼ������BJT�����ġ���BiCMOS������BJT�������������PMOS�ܵ�Դ��©��ͬʱ�γɣ�BJT�����ķ���������NMOS�ܵ�Դ��©��ͬʱ�γɡ���������BiCMOS������������ͼ��ͼ2��ʾ��

����������BiCMOS��·�������պ�ϸ�ӹ����������⿼��

1��˫��ṹ�е���ṹ�ߴ缰�����

��BiCMOS��·��˵����Ҫ��ϸ�о�CMOS���BJT�����ļ��缫�Ĺ���Ҫ��һ����Ҫ�Ĺ���������Է����漰�����Ӳ������������ԡ�����BJT������һ���漯�缫-���伫֮��ķ��������ѹU��BR��CEO�����缫����͵��ݣ��Լ��������յĿɿ����Ծ��������Ӳ����ͺ�ȣ���һ���棬������Ӳ�̫������Ƶ��fT�ͻ��½������缫����RCֵ�ͻ�������MOS������������PMOS����ʱʹ��N+����Ҫ�����Ӳ�����㹻���Ա������Ľ���ݺ�PMOS�����ı�ƫ����ЧӦ��back-bias body effect����

˫��ṹ�е�N�岻��Ӱ��PMOS����������Ҳ����ΪNPN��BJT�����ļ��缫����ˣ�����Ӧ��ֱ�֤CMOS�������������⣬N����Ӽ�Ҫ�㹻���Է�ֹKirkЧӦ��Kirk effect����ͬʱ��Ӧ�㹻�ᣬ������BJT������U��BR��CEO��

2�����Ӳ����Բ���

���������͵��������������ӵı����Ӳ㣬�����ӳ���������˵��һ����ս������ʹ�ڴ�ֱ��ˮƽ����������������ʵ��Բ��Ӿ�����С���Ա�����������Ҫ�����ķ����ӡ�

3��������������ע�뽵��MOS������ֵ��ѹ

��PMOS�����Ĺ�����ͨ��������ע����ڣ���������ֵ��ѹ������NMOS����������ʱע�������ӣ�������ʹNMOS��������ֵ��ѹ��ɢ�Դ�Ϊ��С�����һ��ɼ�СN��ͬP�ͳĵ�IJ���Ũ�ȱ�ֵ����һ������ζ��N��������Ũ�ȿ��Խ��ͣ����NMOS��������ֵ��ѹ��Ϊ��С�����ʹͨ����BiCMOS��·���ڵ͵�Դ��ѹ��3.3V���¹�����

4���ù�դ�Զ����ռ�С��������

����MOS����ʱ���ù�դ�Զ�����դ��Դ��©��������չ�����գ�ʹդ-Դ��դ-©��ɢ�����ص�����С��դ-Դ��դ-©����������Ӧ�ش�Ϊ��С�������������ڹ�դ˫��BiCMOS��·�Ĺ����ٶȵ�����ߡ����⣬��դ�Զ�����Ҳ�����Լ�С���ͬ��������MOS��������Ҫ�İ�ͼ�ߴ磬���оƬ�ļ��ɶȵõ�����ߣ���Լ���30%����

5���øߵ�����P��ĵ�����߹����ٶ�

BiCMOS����Ӧ���øߵ�����P��ĵ棬��������CMOS���伫�������·��ECL�����黯�裨GaAs�����������õļ����ԣ��ֽ�����NMOS�����Ľ���ݣ����������ͨ�ź���Ϣ������BiCMOS��·���ٶȡ���

������ ͨ������������·�����ֲ����������е�

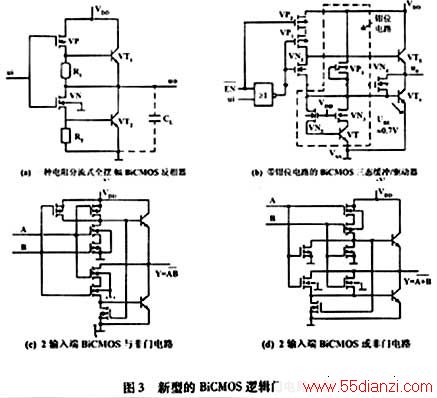

�ɵڶ��ڿ�֪��BiCMOS��·���Ż��������CMOS��·�䵱���ɶȡ����ĵĵ�·���֣�������˫���͵�·��������/�����I/O����·���֣����������BiCMOS���ּ��ɵ�·����Ʒ��������������Ƚ���BiCMOS������BJT����Ҳ���ɵ������С��봫ͳ��CMOS��һ���������ŵ�·����������ַ���ͨ����������BiCMOS���ž�̬���Ľӽ����㣬������ͬ������Ƴߴ��£����ǵ��ٶȽ����졣����BJT�����ļ��������20%��оƬ��������ǿ��ǵ����������������ǿ��BiCMOS�ŵ�ʵ�ʼ��ɶȱ�CMOS�Ž��������ӡ��Ƚϵ��͵�BiCMOS�����У������������ţ�����̬����/������������źͻ���ţ����Ƿֱ���ͼ3��a������b������c������d����ʾ�����������4���ž��ѽ�����Ӳ����·ʵ�飬����ʵ������Ϊ��ƽ�������ӳٽ�Ϊʮ�����룬��̬���Ľ���Ϊ�㣬��̬ƽ������Ҳֻ��1��2mW��

BiCMOS������ͨ�����ֲ����������������������ģ/��ת�����ȣ��������е�Ӧ���м�Ϊ�㷺����Ϊ�����ȳ���һ��Ϊ5��8����˴���ȳ�����ζ�ž��н�ǿ�Ĵ���������������BiCMOS�ű�CMOS���ܸ����ٵ�������Щ���ء����⣬BiCMOS���е������ߴ������һ�µģ���ͽ�����ͨ�����ֲ�������������ϵ��Ѷȣ���ͬ��CMOS��·�Լ�С��λ���صĴ����ӳ�������ͬ��������BiCMOS��·������˫��������BJT����������CMOS��·�������븺�أ�ʹ�ò�ͬ��·�и��ص�״��������ͬ�ģ������ͼ���ͨ�ź���Ϣ�����������������͵�·�������������˹���Ч�ʡ�

������ ͨ���������źŴ�������DSP������������CPU��

��ͨ��DSP��CPU�Ȳ���CMOS���գ���оƬ�����߾�Ҫ�нϴ�Ĵ����ݸ��ص���������ͳ�Ľӿ�������·����˫�������������������Ա�֤���ݴ����ٶȣ����ǹ���ȴ����Щ����32λCPUΪ������������10�����߸���Ľӿ���������ͬһʱ����ֻ��һ�������Ǽ���ģ��༴ÿһ��������90%��ʱ�䲻�������������ֽӿ������ǵ���˫���͵ģ���ʹ���ڹ���ʱ��Ҳ�ڲ�ͣ�����Ĺ��ʣ���������CPU�ľ�̬���Ľ�������

�����BiCMOS�������ɽӿ�������·�����ڷ��Ź���״̬��������ȡ�õĵ�����ҪС���ˡ��ںܶ�����£���̬���Ŀ��Խ�ʡ�ӽ�100%������ͳ���߽ӿ�������·�Ĺ���Լռ����ϵͳ���ĵ�30%�������ֽڵ�Ч���dz�����������ر��������ֻ����������ִ������ͱʼDZ����Ե�һ��ʹ�õ�ص�ͨ�š�������������豸�С���Ϊ�������ǣ�BiCMOS���ּ��ɵ�·���ٶ����Ƚ���˫���͵�·�������£������������ͨ��ϵͳ���ٶ�Ҫ��������Ӧ�ġ�

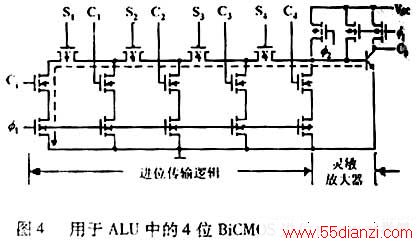

��0.8��m BiCMOS�����Ƴ���ƵΪ100MHz��32λCPU��·���õ�·��CMOS����ռ97%����BJT����ֻռ3%��BJT�����������������ص��ݻ�Ŵ�С�ĵ�ƽ�ڷ��źš�ͼ4Ϊ��������Ԫ��ALU������λһ���BiCMOS��λ�����·��ͼ�Ц�1Ϊϵͳʱ�ӣ���2ΪԤ��ʱ�ӡ�����BJT�����Ĵ��ڣ�Ԥ���ƽ������BJT���������ѹ��������Ԥ���ƽ����Ϊ0.8V���¡���ƽ�ڷ��ļ�С��������߸õ�·�������ٶȡ�32λ�ֳ���ALUҪ����8�������Ľ�λ�����·�������ܴ����ӳ�ֻ��7.2ns������Ҳֻ��ʮ�����ߡ�

���Ĺؼ��֣����ɵ�· ��·����֪ʶ������ѧϰ - ����֪ʶ - ��·����֪ʶ

��һƪ��ͭ������