③由于保护电路吸收的瞬间能量有限,太大的瞬间信号和过高的静电电压将使保护电路失去作用。所以焊接时电烙铁必须可靠接地,以防漏电击穿器件输入端,一般使用时,可断电后利用电烙铁的余热进行焊接,并先焊其接地管脚。

④要防止用大电阻串入VDD或VSS端,以免在电路开关期间由于电阻上的压降引起保护二极管瞬时导通而损坏器件。

(4)CMOS的接口电路问题

1)CMOS电路与运放连接。当和运放连接时,若运放采用双电源,CMOS采用的是独立的另一组电源,即采用如图6所示电路,电路中,VD1、VD2为钳位保护二极管,使CMOS输入电压处在10V与地之间。15KΩ的电阻既作为CMOS的限流电阻,又对二极管进行限流保护。若运放使用单电源,且与CMOS使用的电源一样,则可直接相连。

2)CMOS与TTL等其它电路的连接。在电路中常遇到TTL电路和CMOS电路混合使用的情况,由于这些电路相互之间的电源电压和输入、输出电平及负载能力等参数不同,因此他们之间的连接必须通过电平转换或电流转换电路,使前级器件的输出的逻辑电平满足后级器件对输入电平的要求,并不得对器件造成损坏。逻辑器件的接口电路主要应注意电平匹配和输出能力两个问题,并与器件的电源电压结合起来考虑。下面分两种情况来说明:

①TTL到CMOS的连接。用TTL电路去驱动CMOS电路时,由于CMOS电路是电压驱动器件,所需电流小,因此电流驱动能力不会有问题,主要是电压驱动能力问题,TT L电路输出高电平的最小值为2.4V,而CMOS电路的输入高电平一般高于3.5V,这就使二者的逻辑电平不能兼容。为此可采用图7所示电路,在TTL的输出端与电源之间接一个电阻R(上拉电阻)可将TTL的电平提高到3.5V以上。 若采用的是OC门驱动,则可采用如图8所示电路。其中R为其外接电阻。R的取值一般在1-4.7KΩ。

②CMOS到TTL的连接。CMOS电路输出逻辑电平与TTL电路的输入电平可以兼容,但CMOS电路的驱动电流较小,不能够直接驱动TTL电路。为此可采用CMOS/TTL专用接口电路,如CMOS缓冲器CC4049等,经缓冲器之后的高电平输出电流能满足TTL电路的要求,低电平输出电流可达4mA。实现CMOS电路与TTL电路的连接,如图9所示。 需说明的时,CMOS与TTL电路的接口电路形式多种多样,实用中应根据具体情况进行选择。

(5)输出端的保护问题

1)MOS器件输出端既不允许和电源短接,也不允许和地短接,否则输出级的MOS管就会因过流而损坏。

2)在CMOS电路中除了三端输出器件外,不允许两个器件输出端并接,因为不同的器件参数不一致,有可能导致NMOS和PMOS器件同时导通,形成大电流。但为了增加电路的驱动能力,允许把同一芯片上的同类电路并联使用。

3)当CMOS电路输出端有较大的容性负载时,流过输出管的冲击电流较大,易造成电路失效。为此,必须在输出端与负载电容间串联一限流电阻,将瞬态冲击电流限制在10mA以下。

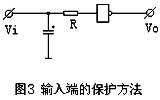

(1)输入端的保护方法。

在CMOS集成电路的使用中,要求输入信号幅度不能超过VDD—VSS。输入信号电流绝对值应小于10mA。如果输入端接有较大的电容C时,应加保护电阻R,如图3所示。R的阻值约为几十欧姆至几十千欧姆。

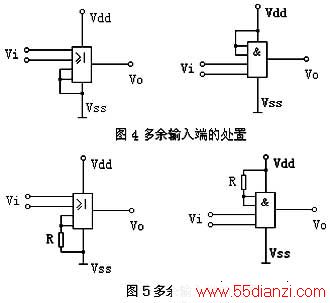

(2)多余输入端的处置。

CMOS集成电路多余输入端的处置比较简单,下面以或门及与门为例进行说明。如图4所示,或门(或非门)的多余输入端应接至VSS端;与门(与非门)的多余输入端应接至VDD端。当电源稳定性差或外界干扰较大时,多余输入端一般不直接与电源(地)相连,而是通过一个电阻再与电源(地)相连,如图5所示,R的阻值约为几百千欧姆。

另外,采用输入端并联的方法来处理多余的输入端也是可行的。但这种方法只能在电路工作速度不高,功耗不大的情况下使用。

在CMOS集成电路的应用过程中,不可避免地要遇到不同类别的器件间相互连接问题。当各器件的逻辑电平互不一致,不能正确接受和传递信息时,要使用接口电路。

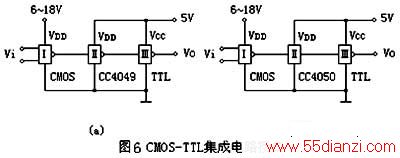

1)CMOS-TTL集成电路的接口

由于TTL的低电平输入电流1.6mA,而CMOS的低电平输出电流只有1.5mA,因而一般都得加一个接口电路。这里介绍一种采用单电源的接口电路。在图6中,门II起接口电路的作用,是CMOS集成电路缓冲/电平变换器,起缓冲驱动或逻辑电平变换的作用,具有较强的吸收电流的能力,可直接驱动TTL集成电路,因而连接简便。但是,使用时需要注意相位问题。电路中CC4049是六反相缓冲/变换器,而CC4050是六同相缓冲/变换器。

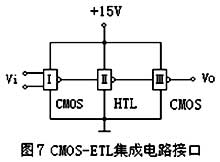

2)CMOS-HTL集成电路的接口

HTL集成电路是标准的工业集成电路,具有较高的抗干扰性能。由于CMOS集成电路的工作电压很宽,因而可与HTL集成电路共用+15V电源。此时,两者之间的VOH、VOL及IIH、IIL均互相满足,不必另设接口电路,直接相连即可,连接电路见图7。

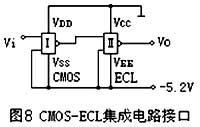

3)CMOS-ECL集成电路的接口

ECL集成电路是一种非饱和型的数字逻辑电路。其工作速度居所有逻辑电路之首。ECL采用负电源供电。CMOS集成电路驱动ECL集成电路可使用单电源工作,如图8所示。ECL集成电路加-5.2V工作电压,CMOS的VDD接地,VSS接至-5.2V。以ECL集成电路CE10102为例,(CE10102内部包括4个2输入或非门),流入ECL的输入高电平电流IIH为265uA,输入高电平电压VIH为-1.105V, 在单电源下CMOS电路可以满足ECL集成电路的输入需要。

所有MOS集成电路(包括P沟道MOS,N沟道MOS,互补MOS—CMOS集成电路)都有一层绝缘栅,以防止电压击穿。一般器件的绝缘栅氧化层的厚度大约是25nm、50nm、80nm三种。在集成电路高阻抗栅前面还有电阻——二极管网络进行保护,虽然如此,器件内的保护网络还不足以免除对器件的静电损害(ESD),实验指出,在高电压放电时器件会失效,器件也可能为多次较低电压放电的累积而失效。按损伤的严重程度静电损害有多种形式,最严重的也是最容易发生的是输入端或输出端的完全破坏以至于与电源端VDD、GND短路或开路,器件完全丧失了原有的功能。稍次一等严重的损害是出现断续的失效或者是性能的退化,那就更难察觉。还有一些静电损害会使泄漏电流增加导致器件性能变坏。

由于不可避免的短时间操作引起的高静电电压放电现像,例如人在打腊地板上走动时会引起高达4KV~15KV的静电高压,此高压与环境湿度和表面的条件有关,因而在使用CMOS、NMOS器件时必须遵守下列预防准则:

(1)不要超过手册上所列出的极限工作条件的限制。

(2)器件上所有空闲的输入端必须接 VDD 或 VSS,并且要接触良好。

(3)所有低阻抗设备(例如脉冲信号发生器等)在接到 CMOS 或 NMOS集成电路输入端以前必然让器件先接通电源,同样设备与器件断开后器件才能断开电源。

(4)包含有 CMOS 和 NMOS 集成电路的印刷电路板仅仅是一个器件的延伸,同样需要遵守操作准则。从印刷电路板边缘的接插件直接联线到器件也能引起器件损伤,必须避免一般的塑料包装,印刷电路板接插件上的 CMOS 或 NMOS 集成电路的地址输入端或输出端应当串联一个电阻,由于这些串联电阻和输入电容的时间常数增加了延迟时间。这个电阻将会限制由于印刷电路板移动或与易产生静电的材料接触所产生的静电高压损伤。

(5)所有 CMOS 和 NMOS 集成电路的储存和运输过程必须采用抗静电材料做成的容器,而不能按常规将器件插入塑料或放在普通塑料的托盘内,直到准备使用时才能从抗静电材料容器中取出来。

本文关键字:集成电路 电路基础知识,电子学习 - 基础知识 - 电路基础知识

上一篇:倍压整流电路