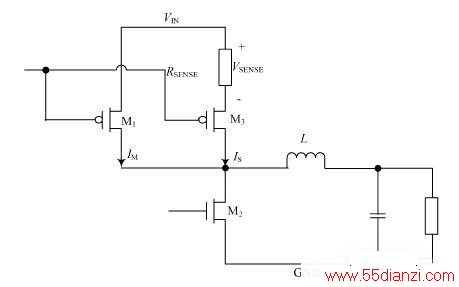

如下图所示,这种检测技术是上一种的改进形式,只不过它的检测器件不是FET而是小电阻。在这种检测电路中检测小电阻的阻值相对来说比检测FET的RDS要精确很多,其检测精度也相对来说要高些,而且无需专门电路来保证功率FET和检测FET漏端的电压相等,降低了设计难度,但是其代价就是检测小电阻所带来的额外功率损耗比第一种检测技术的1/N2还要小(N为功率FET和检测FET的宽度之比)。此技术的缺点在于,由于M1,M3的VDS不相等(考虑VDS对IDS的影响),IM与IS之比并不严格等于N,但这个偏差相对来说是很小的,在工程中N应尽可能的大,RSENSE应尽可能的小。在高效的、低压输出、大负载应用环境中,就可以采用这种检测技术。

上一篇:新型的电流检测方法