全加器电路

点击数:7850 次 录入时间:03-04 11:58:30 整理:http://www.55dianzi.com 电路基础知识

不但完成本位二进制码

ai和

bi相加,而且还考虑到低一位进位

ci-1的逻辑部件称为全加器。它的输入为

ai、bi、ci-1,输出为

si、ci。由二进制加法法则得全加器的真值表如表Z1304所示。

表Z1304 全加器真值表

ai bi ci-1

si

ci

0 0 0

0

0

0 0 1

1

0

0 1 0

1

0

0 1 1

0

1

1 0 0

0

0

1 0 1

0

1

1 1 0

0

1

1 1 1

1

1

由真值表得

si、ci的逻辑表达式分别为:

据此,得到全加器的逻辑图如图Z1306(a)所示。图(b)为全加器的逻辑符号。

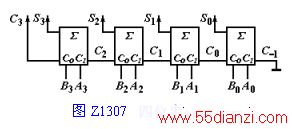

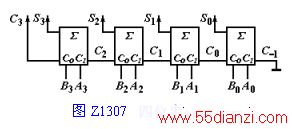

如把多个全加器组合起来,即可完成多位二进制加法。图Z1307表示两个4位二进制数相加的逻辑电路图。

本文关键字:全加器 电路基础知识,电子学习 - 基础知识 - 电路基础知识