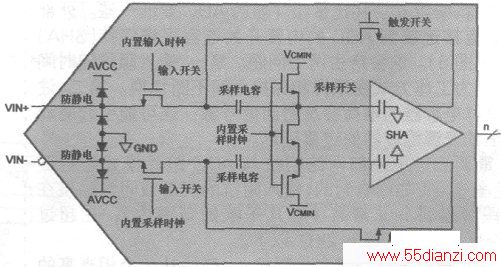

目前流行的CMOS开关电容ADC没有内置的输入缓冲器,所以其功耗比带缓冲器的ADC要低一些。外部信号源直接连接到ADC的内置开关电容采样保持(SHA)电路(见下图)。这会产生两个问题。第一,输入阻抗随时间变化,因为工作方式在采样和保持之间不断切换。第二,注入到采样电容器的电荷会反射回信号源;这可能引起驱动电路里的无源滤波器的过渡延迟。

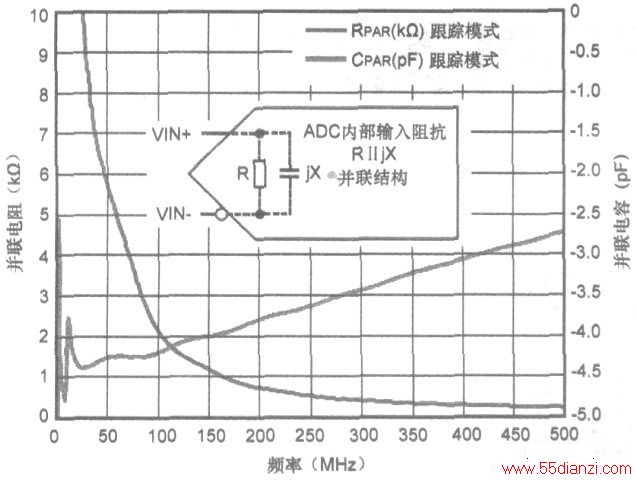

重要的是把外部网络阻抗与ADC跟踪模式阻抗匹配,见下图。正如你看到的,输入阻抗的实部或阻性阻抗在低频段(基带)非常高(在几千欧姆范围内),在超过100MHz的频段下降到2kΩ以下。

输入阻抗的虚部或容性阻抗,一开始从一个相当高的容性负载,然后在高频段减小大约3pF(见右边纵坐标)。要匹配这样的输入阻抗是一个相当具有挑战性的设计问题,尤其是在频率高于100MHz的情况下。

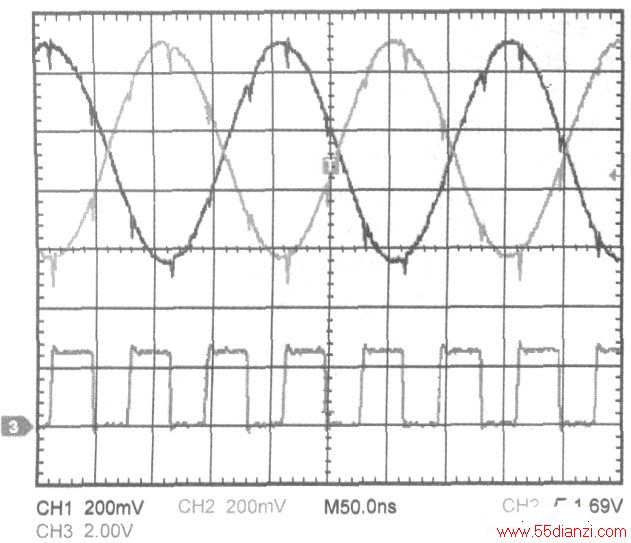

上图和下图中的波形示出了差分输入信号的优势。上图中示出的ADC的单端输入波形看起来很差。但是,下图明了单端输入波形受到的干扰几乎完全是由于共模电压的影响。

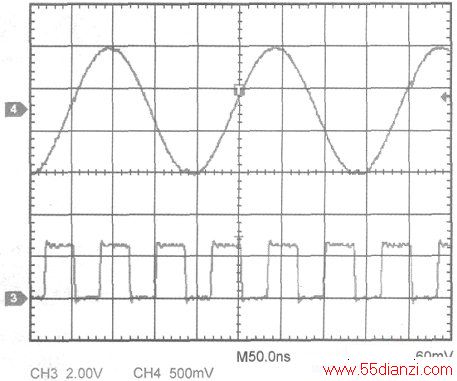

见ADC的差分输入(见上图),我们可以看到输入信号干净多了。与时钟相关的尖峰干扰消失了。差分信号固有的共模抑制特性能够消除共模噪声,包括来自电源、数字源和电荷注入引起的共模噪声。

带输入缓冲器的ADC比较容易理解和使用。输入源阻抗固定。缓冲器由晶体管组成,它以低阻抗驱动ADC,所以大大地减少了注入电荷和开关管引起的尖峰。与带开关电容的ADC不同,输入阻抗在模拟输入频率范围内变化很小,所以选择合适的驱动电路相对容易一些。带缓冲器的ADC特别适合于高线性、低噪声应用;它唯一的缺点是由于它自身的功导致ADC总功耗增加。

本文关键字:放大器 电路基础知识,电子学习 - 基础知识 - 电路基础知识

上一篇:集成运算放大器开环电压增益的实现