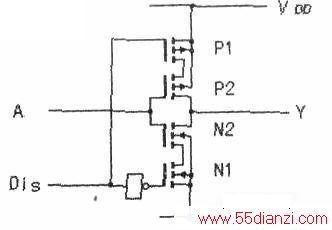

1.控制上下P/N沟道的截止或导通,实现三态输出功能

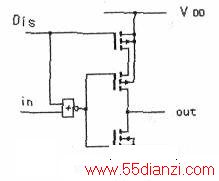

基本线路如下图所示,图中的P2与N2组成反相器;P1与N1组成三态控制开关。当Dis输入端为“H”(逻辑高电平)时,P1与N1同时截止,输出呈现高阻状态;当Dis输入端为“L”(逻辑低电平)时,P1与N1同时导通,输入与输出之间可以执行逻辑反相功能。

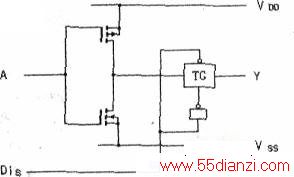

2.在输出端串联传输门开关的三态线路图

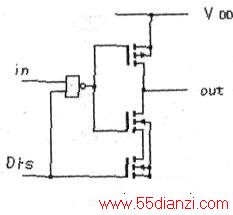

上图示出了用传输门作为三态电路的形式。

当三态控制端Dis为高电平“H”时,传输门TG断开,这时传输门的输出呈高阻;而当三态控制端为“L”时,传输门TG接通,此时传输门的输出呈低阻。传输门传输门的逻辑状态取决于反相器“F”的输入状态。因此,传输门的输出端可以挂接总线。

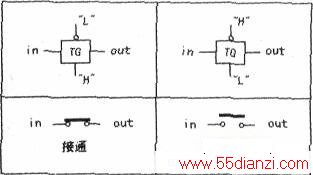

下图示出了传输门的符号和含义。

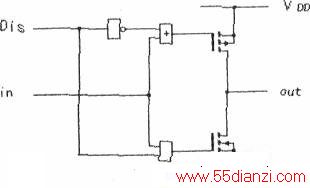

3.利用或非门或者与非门实现三态功能

两个MOS管的栅极分别受门电路控制,如上图所示,图中当三态控制端Dis为“L”(低电平)时,两个串接MOS场效应管均断开,输出高阻;当三态控制端为“H”(高电平)时作为控制两个串接MOS管的门电路均处于允许状态,于是电路的输出取决于输入状态。

将上图的三态电路略加变形,就可以增加三态电路的驱动能力,大吸收驱动电流三态电路如中图所示,大输出驱动电流三态电路如下图所示。

本文关键字:暂无联系方式数字电路,电子学习 - 基础知识 - 数字电路

上一篇:什么是CMOS信号/TTL信号