在电子技术实验教学中,构建的电路设计理念,提高的电路设计能力,是教学的根本目的和核心内容.数字钟电路的设计包括了时序逻辑电路.组合逻辑电路.数码管显示电路和脉冲信号产生电路等内容,内容涉及面宽.综合性强,是电子技术自主性实验教学的典型案例.文中采用了石英晶体振荡器电路.计数电路.动态扫描及译码驱动电路.显示电路和时钟校正电路,来实现该电路.

1 系统设计方案

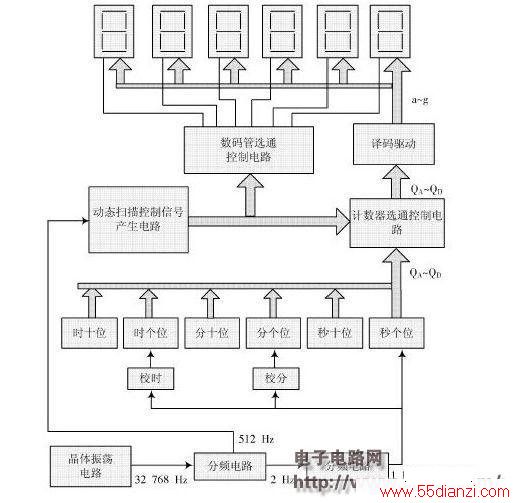

本次设计的数字钟,实现对时.分.秒的数字显示,周期为24 h,显示满刻度为23 时59 分59 秒,并具有校时功能.电路主要采用中规模CMOS集成电路,采用电池作电源,通过共阴极LED 数码管显示时钟.该系统由秒脉冲产生模块.计数器模块.译码显示电路模块.动态扫描模块.校时模块组成.其中秒脉冲产生模块由晶体振荡器电路和两个分频器电路组成,动态扫描模块由动态扫描控制信号产生电路.计数器选通控制电路和数码管选通控制电路三部分组成,系统组成框图如图1所示.

1.1 秒脉冲产生电路

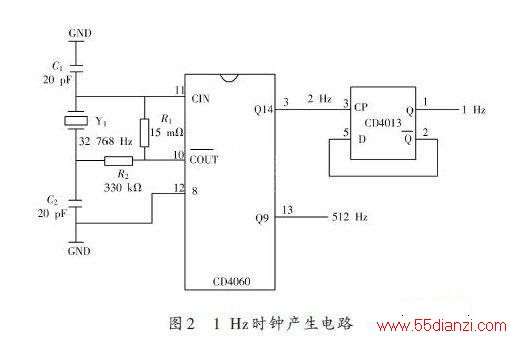

秒脉冲信号由石英晶体振荡器产生,由于晶体振荡器输出频率较高,为了得到1 Hz 的秒信号,需要对振荡器的输出信号进行分频.通常的分频器采用多级二进制计数器来实现.将32 768 Hz 的高频方波信号经32 768(215)次分频后得到1 Hz的方波信号供秒计数器进行计数,即实现该分频功能的计数器相当于15 级二进制计数器.

本次设计采用CD4060 来构成14 级2 分频电路.

CD4060的9脚.10脚.11脚内含两个非门电路,1脚输出12分频信号,2脚输出13分频信号,3脚输出14分频信号.利用CD4060的两个非门和32768Hz的晶振构成32 768 Hz 的振荡器,然后通过CD4060 进行214 分频得到2 Hz的信号,再经过D触发器CD4013进行一次二分频即可得到1 Hz的秒脉冲.电路图如图2所示.

1.2 计数器设计

计数器电路用来完成60 秒60 分及24 小时的计数工作,且秒计数器的进位脉冲作为分计数器的输入脉冲,同理分计数器的进位脉冲作为小时计数器的输入脉冲.“ 秒”.“ 分”.“ 时”计数器电路采用同步加计数器CD4518来完成.

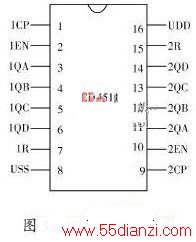

(1)CD4518双BCD同步加计数器

CD4518 是一只双BCD 十进制计数器,它含有2 个独立的计数单元,有2个计数脉冲输入端,上升沿触发端CP 和下降沿触发端EN,若用CP 来触发,则EN 接高电平,且为上升沿触发;若用EN 来触发,则CP 接低电平,且为下降沿触发;有4个输出端QD~QA,一个清零端.

CD4511的引脚图如图3所示.其中:

CP:时钟输入端,上升沿触发;

EN:时钟输入端,下降沿触发;

R:复位端,高电平时计数器=0;

QD~QA:计数值十进制输出端;

UDD:正电源输入端(3~15 V);

USS:电源参考地.

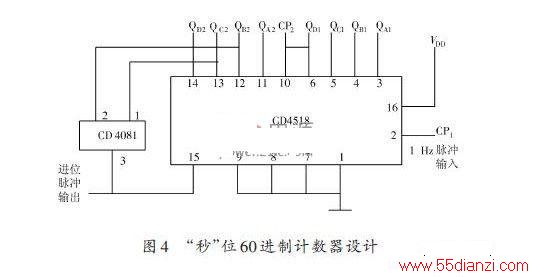

(2)“时”.“分”.“秒”计数器设计

把CD4518 内部的两个十进制计数器级联构成100 进制计数器,然后通过反馈法实现60进制计数器,电路如图4 所示.图中,QD1,QC1,QB1,QA1 为秒个位的二进制BCD 码,QD2,QC2,QB2,QA2 为秒十位上六进制BCD码,当十位要显示十进制6时即0110,此时QC2.QB2均为1,经CD4081(42输入与门)输出也为高电平,其他时候为低电平,利用这个脉冲信号给十位计数器清零,同时这个脉冲信号也是分脉冲的输入信号.

分计数器与秒计数器电路完全相同,只是脉冲输入不同,秒计数器是1 Hz,而分计数器是1 60 Hz.

时计数器为24 进制计数器,设计原理与分秒计数器相同,不同之处在于反馈清零的状态不同,当十位(显示2).个位为0100(显示4)时对计数器全部清零.把QB2 和QC1 通过CD4081 相与送给两个十进制计数器的复位端即可.

1.3 数码显示及动态扫描电路

数码显示器采用共阴极LED数码管.译码显示驱动电路选用BCD-7 段锁存译码/驱动器CD4511.数码管多位显示是可以采用两种驱动方式:一种是静态驱动,静态驱动方式是对各位显示器连续地施以驱动电压,使显示器持续点亮的方法.每一位显示器都要配备一套包括计数器.译码器和驱动电路.静态驱动的原理相对简单,适用于位数不多的场合.当位数较多时,使用元器件增加,功耗也大.另外一种方式为动态驱动,动态驱动方式是用扫描方式让各位数码管按一定顺序轮流显示的方法,其优点:第一,能降低功耗,这对电池供电的便携式数字仪表尤为重要;第二,各位显示器共用一个译码器,节省了译码器的数量,减少连线;第三,能输出多路BCD 码,容易和计算机相连.只要扫描频率足够高,由于人眼的暂留效应就观察不到闪烁现象.

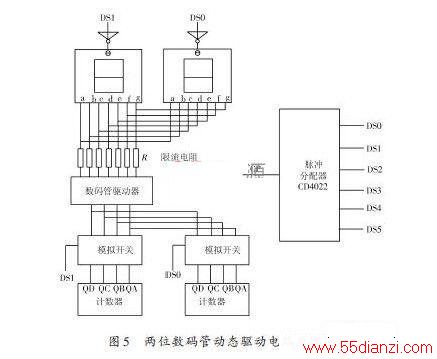

动态扫描的总体特点是位扫描,段选通驱动.本次设计采用动态扫描方式,两位LED 显示器动态驱动原理图如图5所示.

采用脉冲分配器CD4022 产生动态扫描信号DS0~DS5,这6 个信号在同一时刻只有一个为高电平,利用DS0~DS5 控制模拟开关CD4066,当某个扫描信号为高时,所控制的四路模拟开关导通,从而把对应计数器的数据送给译码驱动电路,同时扫描信号要选通对应的数码管显示相应的数据.由于采用的是共阴极数码管,因此扫描信号通过达林顿晶体管整列MC1413 才能选通对应数码管,当某扫描信号为高时,经过MC1413 输出后变为低电平所对应数码管被点亮.脉冲分配器CD4022 的输入脉冲CP 的频率应该足够高,这里选用512 Hz(由4060第13脚提供).

1.4 校时电路

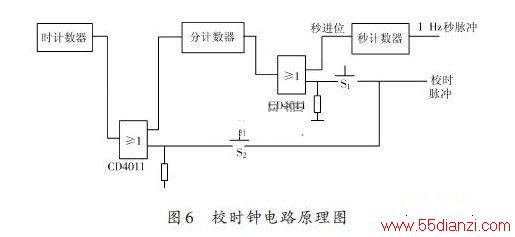

校时是数字钟应具备的基本功能,当数字钟接通电源或有时.分.秒等校正功能.为使电路简单,这里只进行分和时的校正.校正电路的要求在校正时位时不影响分和秒的正常计数,在校正分位时不影响秒和时的正常计数.

校准的方法很多,常用的有“快速校时法”.校时电路原路图如图6所示.

2 结语

数字钟电路的设计,涉及模拟电子技术.数字电子技术等多方面知识,将其列入自主实验内容,克服了以往实践教学形式单一.内容简单枯燥的缺点[8].实验过程中要求独立完成设计.可以采用万能板焊接完成数字钟电路的制作,也可以绘制PCB电路图采用热转印的方法自制PCB电路板完成该电路的制作.

上一篇:电风扇自动控制器