【摘要】将LED 显示屏的特点和自由立体显示的视觉效果相结合,采用特殊的LED 立体显示屏,利用片上系统(SoC)和可编程片上系统(SoPC)的设计方法,提出立体LED 显示屏控制系统的完整设计方案。在LED 时序发生器的设计中利用直接内存存取(DMA)传输技术,生成队画面数据,用改进型的D/T 转换技术控制所有像素点的亮度。结果表明,本设计借用了立体液晶显示的解决方法,在LED 显示屏上实现了自由立体显示,保证了屏幕的刷新速率,同时还降低了立体真彩显示系统的复杂性。该设计方案能够保证画面有效实时显示,具有较强的实用性。

1 引言:

LED视频显示屏由于亮度高、视角广、寿命长、功耗低、性价比高,而且具有可与计算机同步显示各种文字、图形、图像,可实时播放电视、录像、影碟等视频信号,可即时输入、编辑各种多媒体数据等优点,使其在街头、广场、商业中心、运动场所、娱乐场所、控制中心等许多公共场合得到了广泛的应用。

随着人们对视觉要求的不断提高,如何在LED 大屏幕上实现自由立体显示成为急待解决的问题。为此,笔者提出了一种新的解决方案,使得在LED 显示屏上实现自由立体显示成为可能,同时还降低了立体真彩LED 显示系统的复杂性。

2 系统硬件设计:

由自由立体显示原理可知,要实现LED 立体显示除了有立体信号源,对外还需要有自由立体LED 显示屏和控制系统。由于自由立体显示的一帧画面需要一对图像数据,和现有的LED 大屏幕显示器相比,要达到同样的显示规模其显示数据量增加一倍,扫描速度也增加一倍,因此选择ALTEra 的Nois 结构。该结构的特点是具有嵌入式系统IP 软核,含有很多接口模块,包括可配置高速缓存模块、SDRAM 控制器、DMA、定时器、协处理器等。在植入(配置进)FPGA 前,用户可根据设计要求,利用QUARTusⅡ和SoPC builder,对Nois 及外围系统进行构建,使该嵌入式系统在硬件结构、功能特点、资源占用等方面全面满足用户设计系统的要求。特有的Avalon 总线结构通信接口,使用户可随意配置32/16 位总线指令集和数据通道。

同时Avalon 的流模式结构还能在没有CPU 干预的情况下自动按顺序进行数据传输,提高运行速度,因此充分满足自由立体LED 显示器对速度的要求。

2.1 LED 立体显示屏的设计:

自由立体显示是基于双目视差原理实现的, 有4 种不同格式的图像源,分别是SS 格式、TB 格式、FS 格式和FrS 格式。SS 格式为左、右视图列交叉显示;TB 格式、FS格式为左、右视图行交叉显示;FrS 格式为第1 帧奇数列、第2 帧偶数列列交叉显示。对应4 种不同的3D 模式,其数据存储方式也有所区别。根据人类的视觉原理和SS 格式,本设计的LED 自由立体显示屏设计成由特殊排列的红、绿、蓝子像素构成,红、绿、蓝子像素的排列在水平方向上为自左至右均匀间隔排列构成一个水平行,在垂直方向上为红、绿、蓝子像素各构成一个垂直列,同样均匀间隔排列。显示屏上放置一块光栅板,利用该光栅板保证观察者通过光栅左眼只能看到显示单元显示的左眼图像,而右眼只能看到显示单元显示的右眼图像,从而获得不用佩带眼镜就可以观看的自由立体图像,通过FPGA 控制器驱动显示自由立体动态图像。

2.2 FPGA 结构设计:

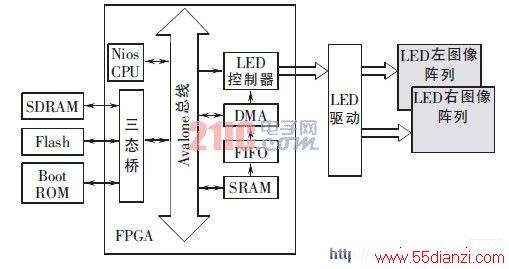

本系统采用可以在线配置Nios 软核的FPGA 芯片EP1C6QC240C8。系统根据自由立体LED 的要求利用Avalon 总线配置了32 位CPU 软核以及ROM,RAM,SRAM,FIFO,SDRAM 和DMA 等片内外资源, 用以存储和快速传输数据, 同时还专门设计了LED 控制器以实现自由立体LED 显示功能。

图1 FPGA 系统结构图

www.55dianzi.com

系统硬件结构如图1 所示。Nios Ⅱ主端口的时钟是内部总线的时钟,本系统采用50 MHz,用流模式传输的最大带宽能达到100 Mbit/s。在电路设计时,首先用硬件描述语言写用户逻辑,创建Alvalon Slave 接口使之直接和DMA 控制器的主端口相连接, 完成硬件设计。再在Nios Ⅱ IDE 环境下,用C 语言编写DMA 初始化和控制程序,使得流模式的数据传输在FIFO 与Avalon 总线的接口上,能够做到无缝连接。

2.3 立体LED 控制器的设计:

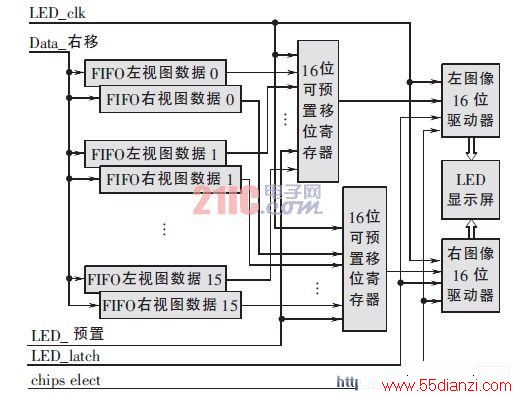

Avalon 流模式LED 控制器硬件结构如图2 所示,用硬件描述语言设计LED 时序发生器, 由于LED 各个像素点的色彩是以RGB 形式的亮度数据用二进制数字方式存储在SDRAM 中的,使用D/T 转换技术[5]即亮度时间转换技术就可以实现LED 屏的全彩显示。笔者设计了一个专用的函数f(i),用此函数即可统一控制各个像素点实现全屏幕所有像素点相互独立而又同步的D/T 转换。这里,f(i)作为LED_latch 信号。

图2 Avalon 流模式LED 控制器结构图

因为FIFO 中的数据格式是左、右视图列交叉显示,因此LED 控制驱动器的设计是以列驱动的。LED 时序发生器的设计如图3 所示,将立体图像对中左、右眼图像帧每个像素的数据用乒乓开关控制存储在FIFO 缓存之中,以16 个列像素点的驱动为例,FIFO 缓存之中的左、右视频数据分别各连接一个16 位可预置移位寄存器,通过16 个时钟脉冲的移位产生16 个像数的驱动数据,由片选信号选择显示行数,由D/T 转换函数f(i)作为LED_latch信号锁存,FIFO 缓存的数据经过8 次移位即可完成1 个像素的真彩驱动。

图3 LED 时序发生器内部结构图

每帧画面显示1 个立体像素真彩信号的时间需要移位8 次, 即250 个基本周期。如果LED 大屏幕显示器每秒最多显示30 帧, 采用1/8 驱动模式和立体像素的1/2时分复用, 再考虑选用16 位移位锁存LED 恒流驱动电路,实际要求的时钟频率为2 MHz。

3 系统软件设计与仿真:

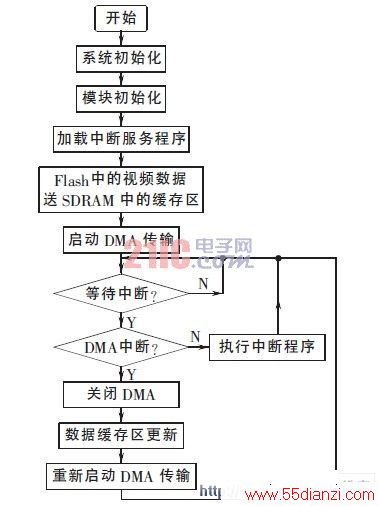

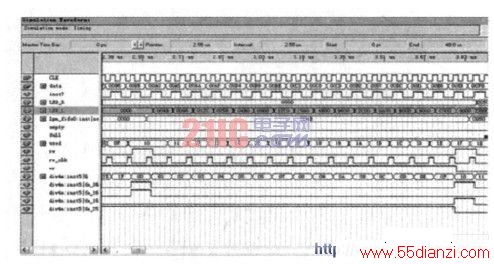

软件设计就是利用SoPC Builder 生成软件文件,用文本编辑器编写汇编语言或C/C++源程序,用GUNPro 将源程序编译成可执行文件, 并通过下载电缆对可执行程序进行调试和运行。软件系统分为两部分:主程序和中断服务程序。主程序主要完成系统的初始化,其主要功能是:对于系统中的每一个微处理器,从设备都生成一个定义该设备地址的头文件,为软件开发创建存储器映射文件。DMA 的操作都通过中断服务程序执行,把需要送出的像素信息排成一行顺序送出形成数据流,借助于Avalon 流模式外设的设计方法, 实现一个Avalon 流模式的LED 控制器。利用DMA 控制器在流模式控制器和SRAM 之间建立一条DMA 传送通道, 让硬件来完成像素信息的自动读取。软件流程如图4 所示,部分内部时序仿真如图5 所示。

www.55dianzi.com

图4 软件流程图

4 小结:

在本文的设计中,利用SoPC 解决方案,选用Nios Ⅱ32 位处理器,根据人类的视觉原理,将3D 立体显示SS格式数据在专门设计的带有光栅的LED 立体显示屏上显示出来。采用了Avalon 总线的流数据传输结构极大地提高了数据处理的速度,加快扫描频率,同时专门设计了改进型的D/T 转换技术, 使得系统只使用一个函数就实现了所有像素点亮度的控制,极大地降低了LED 时序电路发生器的复杂性。通过系统仿真得到了相对满意的效果。但是在设计过程中发现,LED 大屏幕显示器前的光栅设计极为关键,包括与显示屏的距离、光栅的具体尺寸、观看的距离以及其间的相互关系等还有待进一步研究。

本文关键字:驱动器 显示电路-显示屏,单元电路 - 显示电路-显示屏