通常扩频通信系统的解调电路很复杂,本系统为了使解调电路简单化,采取基带信号速率与扩频码元周期同步同速的特殊措施,省去了解调电路中复杂的载波恢复电路。直接序列扩频通信系统中,接收端与发送端必须实现载波同步、PN码同步,才可以正常工作。同步系统是扩频通信的关键技术。

1 本扩频系统的调频解调原理

本系统的载波,PN码和基带信号的速率来自于同一个时钟源,而且载波频率和PN码频率都是基带信号速率的整数倍,所以系统在解调端获得PN码同步的同时,也获得了载波的同步。

2 系统总体设计及参数选择

本系统设计其顶层采用图形设计方式,各模块基于Verilog HDL设计。图1为系统模块图。

基带数据的码速率为0.806 Kb/s,PN码速率为25 Kb/s,基带信号与PN码相异或输出信号去调制载波产生BPSK信号,载波的中心频率为100 kHz。本系统调制电路各部分的时钟源参数依据系统框图选择,晶振频率是50 MHz,以上各部分的时钟经分频后得到。

3 模块设计及实现

3.1 分频模块

本系统发射的基带数据速率是0.806 Kb/s,PN码的频率是25 kHz,正弦波的频率是100 kHz,所以整个系统所需的时钟为50 MHz,PN码所需的时钟是25 kHz,基带信号所需的时钟是0.806 Kb/s。为了更好地实现同步,后面两者分别经过16×125分频,31×16×125分频得到,分频器通过编程实现。时序仿真如图2所示。

3.2 PN码发生器模块

采用最大长度线性反馈移位寄存器(m序列)生成扩频码字,其本原多项式如下:

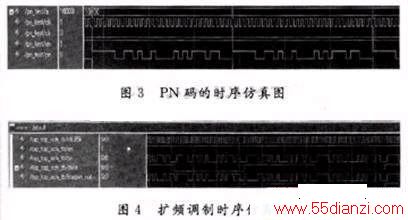

PN发生器的时序仿真如图3。产生的25-1位PN码为:

[ 1 1 1 1 1 0 0 1 1 0 1 0 0 1 0 0 0 0 1 0 1 0 1 1 1 0 1 1 0 0 0 ]

3.3 直接序列扩频模块

直接序列扩频的实现比较简单,用PN码与信息序列模二相加(波形相乘),对基带信息进行扩频调制。本设计采用31位的PN码,需要满足如下关系Tc=31Tb(Tc为基带信号周期;Tb为PN码周期)。扩频调制的时序仿真如图4所示。

3.4 BPSK调制模块

本系统数字正弦发生器采用了直接数字频率合成(DDS)技术。DDS由相位累加器、相位加法器、波形存储器(ROM)组成。其中,ROM中存放经过采样、量化处理后的周期连续信号一个周期波形的幅度值。在具体实现中ROM表采用了10位,即1 024个采样点。利用DDS产生100 kHz的载波,对扩频信号进行调制。

因此,在本设计中,BPSK的调制通过对扩频模块产生的序列对两路相移为180°的正弦波进行选通来调制,在前面利用DDS产生了两个正弦波的ROM表,通过扩频序列对两张表的数据进行选通,则所输出波形能够实现BPSK调制。

在本设计中,扩频信号与BPSK调制信号的对应关系为:“1”对应180°;“0”对应0°。所以,当数据为1时,选择正弦波的初始相位为180°;当数据是0时,选择正弦波的初始相位是0°,这是通过Verilog编程实现的。

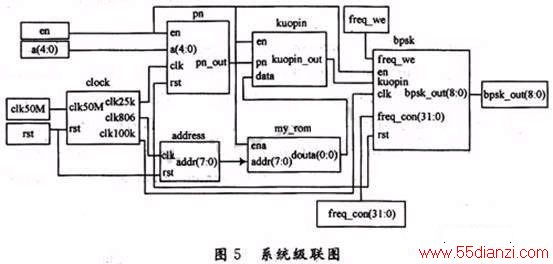

4 系统联合仿真

对各个子模块设计仿真完之后,把各个模块进行级联仿真调试。顶层模块采用原理图输入法,该方法具有直观清晰的特点。系统级联图如图5所示。

系统级联的时序仿真如图6所示。

5 结语

在FPGA芯片上实现了直接序列扩频发射系统,由于所有模块都集成在一个芯片中,提高了系统的稳定性和可靠性。且由于FPGA是一个完全的硬件构架,其中的电路全部由与非门实现,比用传统的扩频系统处理速度更快,并且系统可以通过编程来修改升级,具有很大的灵活性。最后,因载波频率和PN码频率都是基带信号速率的整数倍,所以,系统在解调端获得PN码同步的同时,载波也获得了同步,这样就大大降低了后端解调器的复杂度,具有实用价值。

本文关键字:通信 调制与解调电路,单元电路 - 调制与解调电路

上一篇:由MC1495构成的平衡调制电路