我们在用高于常见的电源电压(如24V)设计逻辑电路时,可以结合使用标准逻辑系列与一只稳压器,通过电平转换器做接口。

另外,如果逻辑并不太复杂,速度也不是非常高,可以用分立元件建立门控电路.直接用当前电压运行。分立元件的与门、或门和非门功能都相对简单明确,但异或门和异或非门功能通常需要多个与门、或门和非门基础功能的组合。

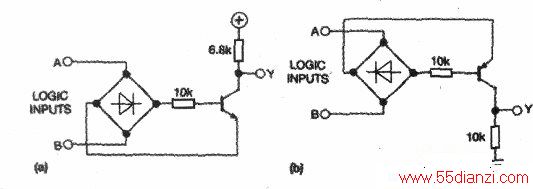

下面给出了一种不常见方法,用两只电阻、四只二极管和一只晶体管,就能完成异或功能。NPN结构获得的是异或非门运算,而PNP结构则得到异或门运算。

考虑附图a中的异或非门电路。当A或B两个门的输人为相反逻辑态时,基射结上有一个高电压压降减低电压再减1.2V,得到的电压做正偏。晶体管导通,集电极的逻辑零电压大约为0.6+VL+VCE,其中VL为低电压,VCE是集射电压。当输入A和B为相同逻辑态时,晶体管基射结不能正偏,因此输出Y为电源电压。

集电极上6.8kΩ的选择要看驱动A和B输入端的是标准TTL逻辑还是CMOS逻辑,可根据应用来选择。CMOS4000系列能够在5v电源下可靠地供出或吸入1mA,低速TTL可以供出0.4Am,吸入8mA。对于基极电流,一个0.4mA的逻辑1驱动电流就足够了,但是A或B端的逻辑O形成了射极电流,CMOS的1mA吸人电流极限就成问题了。在有1mA净电流,输出负载维持在大约250uA时,必须选择一只6.8kΩ电阻才能获得大约5V压降。

然后,考虑异或门结构,此时无论A或B的逻辑O都是相对基极,而逻辑1是相对射极。Y上的逻辑1电压为VH-0.6V-VCE,而逻辑O约为0V,但通过集电极电阻限制了电流。

这里的问题是,rrrL逻辑l的输出电流大约为0.4mA.这是晶体管的射极电流。集电极电阻选10kΩ时,其电压降可以达到近4V。这个电平足以驱动CMOS负载,但对TTL则不然,当Y为逻辑0时,其逻辑O的输入至少需要0.4mA的电流。10kΩ无法提供这一电流。但是,采用前面的异或非门结构,并在Y后另加反相晶体管,就得到了异或门功能附图b)。异或门似乎只适用于A和B端的CMOS/TTL输入,只能在输出Y驱动CMOS。

本文关键字:门电路 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:微处理器选择的脉宽控制器电路