2. 变模可逆分频器的工作原理

变模分频器的基本原理是设置一个符合函数,在分频过程中,触发器的输出与预置模比较,当触发器的输出与预置模一致时,则给出符合信号,强迫计数器进入所希望的状态,即初始状态,随后计数器则按照卡诺图确定的程序继续工作,直到最后一个状态,即由地址码确定的第N-1 个状态,再强迫分频器回到初始状态[3]。所以每个触发器应当受到两个控制函数的控制,即:

f—正常的由卡诺图得到的控制函数;

F—强迫分频器进入的希望状态;

T—符合函数;

当符合函数T = 1时,F 不起作用,P = f ,分频器按正常程序分频;当T = 0,F 起作用,P = F ,强迫分频器跳变到所希望的状态。

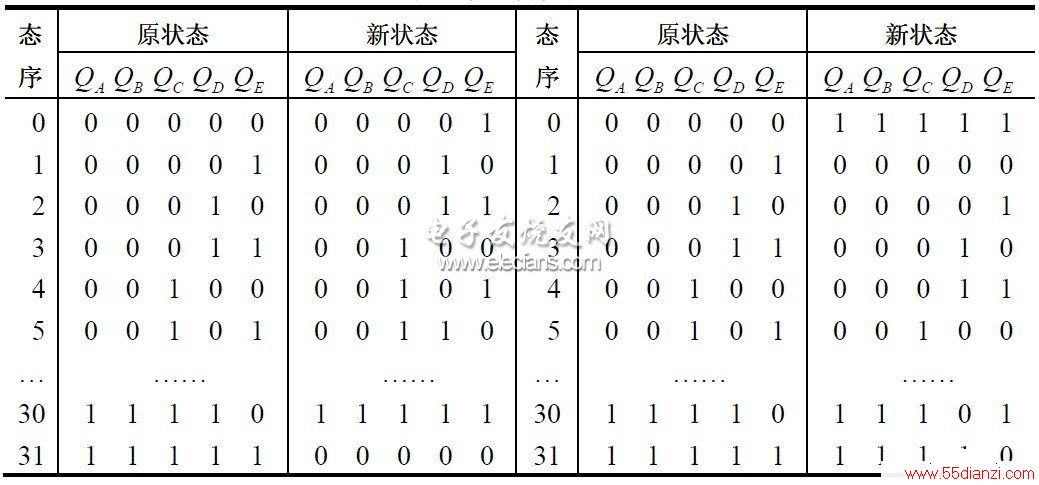

表1 状态转换表

(注:表1 为状态转换图,其中左半部分为递增分频器状态转换表,右半部分为递减状态转换表。表2 为计数值与各触发器当前值的关系。)

表2 计数值与各触发器当前值的关系

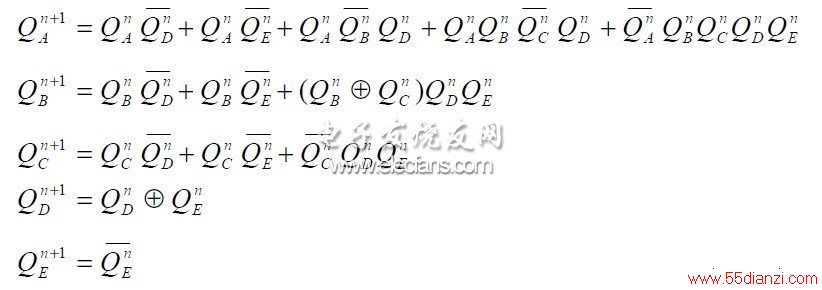

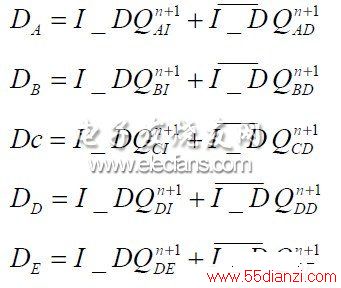

加法分频器的驱动方程为:

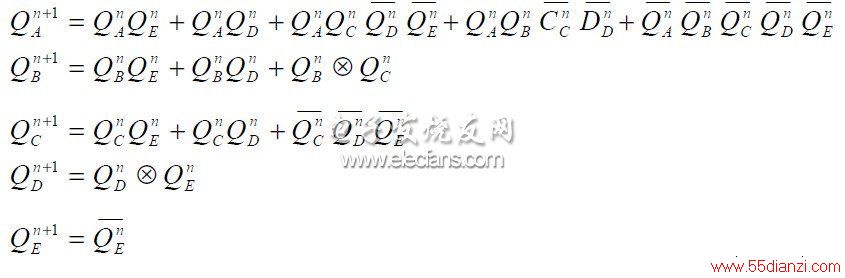

减法分频器的驱动方程为:

各触发器还受到可逆信号的控制,当I _ D信号为1时为递增分频器,反之为递减分频器。

各触发器的驱动函数为:

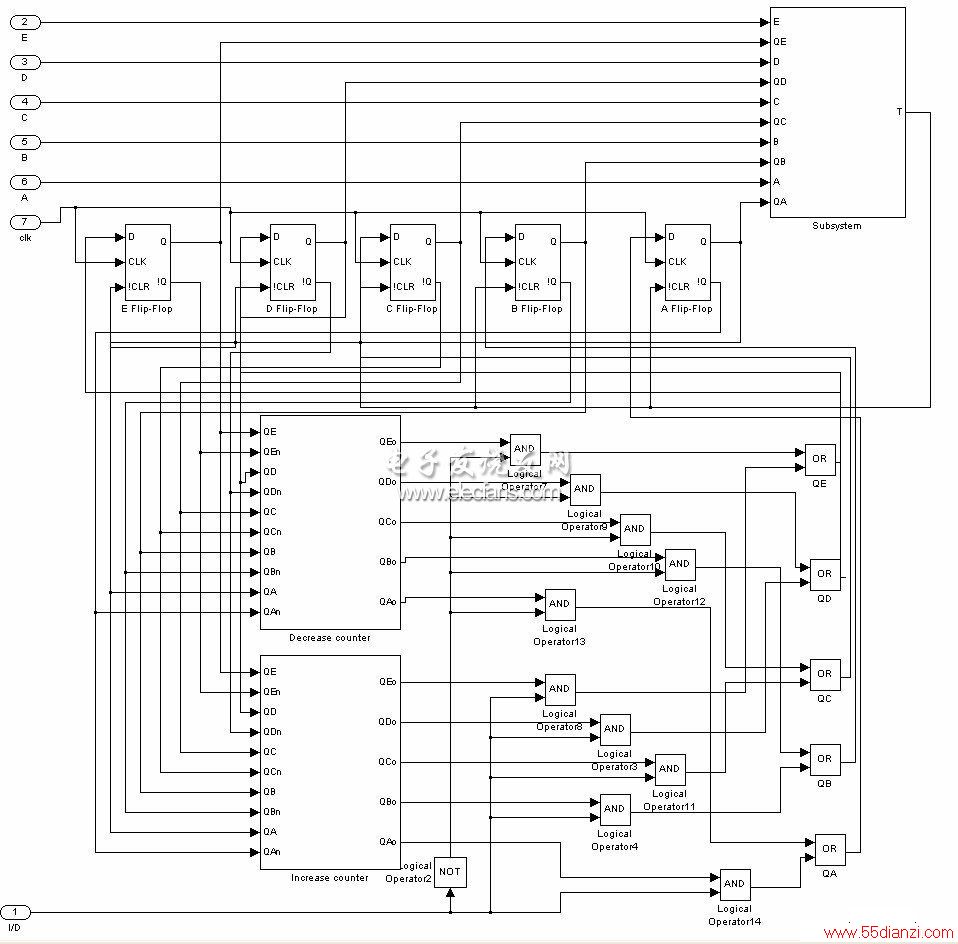

图1 五级分频器

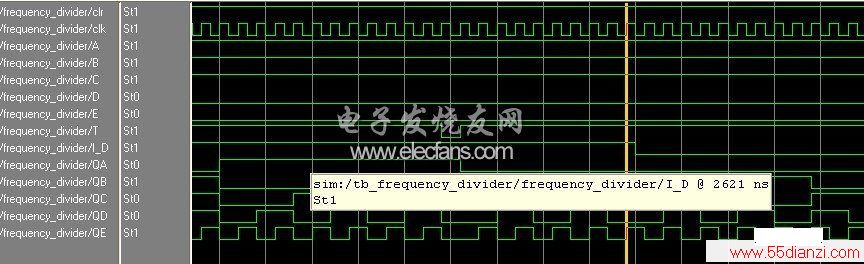

图2 分频器的工作波形。

图3 分频器的仿真波形。

4. 基于FPGA的可逆分频器设计

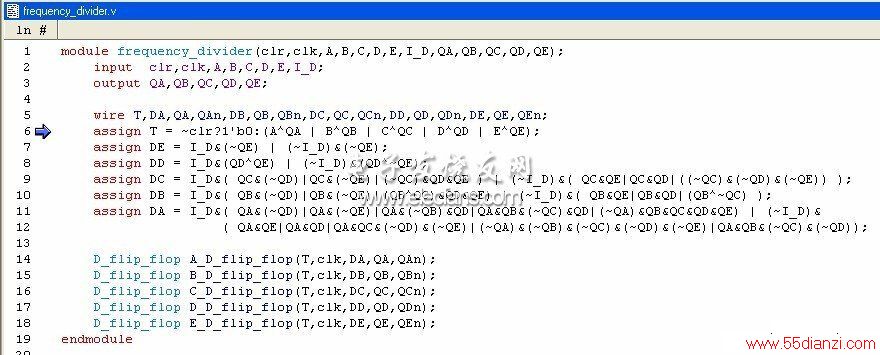

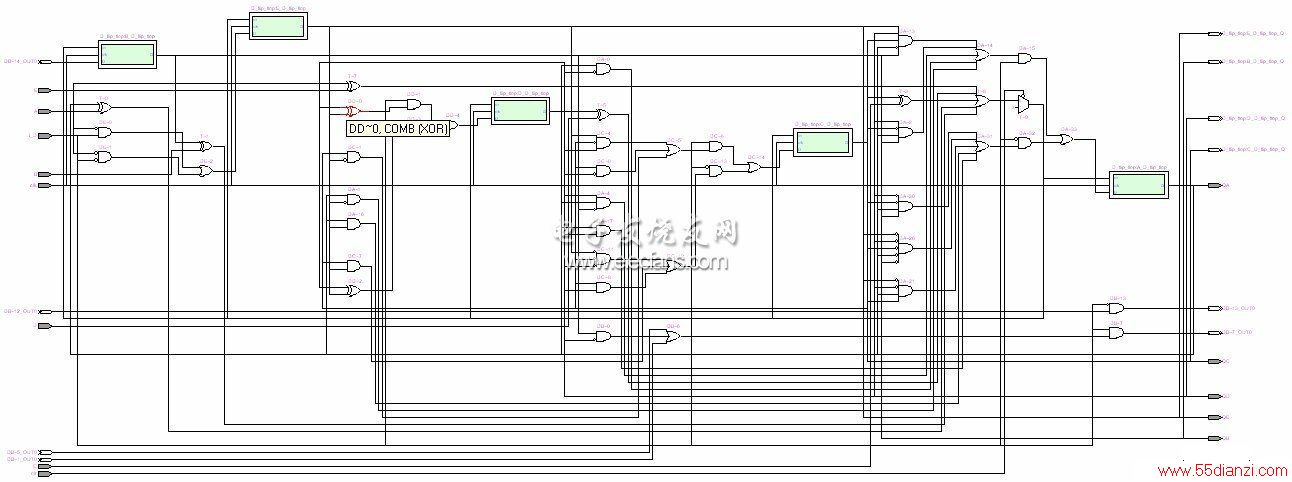

采用verilog 语言实现了可逆分频器,其仿真波形如图3 所示,分频器可完成预置模以及递增及递减分频功能。分频器的verilog 代码如图4 所示,寄存器传输级网表如图5 所示。

图4 分频器代码。

图5 寄存器传输级网表。

5. 总结

本文分析了变模可逆分频器的工作原理,并分别采用simulink 和FPGA 实现了可逆分频器。仿真结果表明分频器能够完成预置模,递增和递减分频功能,满足设计要求。

本文关键字:分频器 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:N进制异步计数器设计方案