引 言

电荷耦合器件(CCD)现在广泛应用于天文图像。

传统的CCD读出较慢且在高帧率的情况下有很高的读出噪音,这限制了它在高时间分辨率天文学的应用。

21世纪初,英国的E2V 公司和美国TI公司各自独立地研发了一种具有新型读出结构的CCD 器件,即电子倍增CCD(EleCTRon Multiplying Charge CoupLED DevICe),简记为EMCCD.这是新一代高质量微光成像器件。与传统的CCD相比,它采用了片上电子增益技术,利用片上增益寄存器使图像信息在电子转移过程中得到放大,这使得它在很高的读出速率下仍具有相对很低的读出噪声,能在微光源下高分辨率成像。

EMCCD 的这些特性,使得它能对微弱光信号进行快速的成像。近年来EMCCD被越来越多地运用到了天文观测,国外研究人员采用E2V 公司的EMCCD 器件L3 VISION CCD设计的相机取得了极好的观测效果,并进行了光子技术成像实验。而国内对天文用EMCCD相机的研制与应用还处于起步阶段。目前,实验室正在研制一套基于EMCCD的二维天文光子计数实验成像系统,该成像系统可使用TI公司的EMCCD 器件TC253和TC285作为图像传感器。

本文针对使用TC253器件构成的图像采集系统,主要介绍EMCCD的数字控制方案和设计方法。由于硬件系统使用ALTEra公司EP3C16Q240C8N FPGA芯片,所以该数字系统是在Altera QUARTus Ⅱ 8.0开发环境下采用VHDL语言来进行设计并实现整个系统的数字控制部分。本文阐述了该数字控制系统的设计思想以及VHDL 的实现过程,给出了关键信号的仿真与实测波形,并对结果进行了分析。

1 EMCCD图像传感器与模拟信号处理器的

控制要求

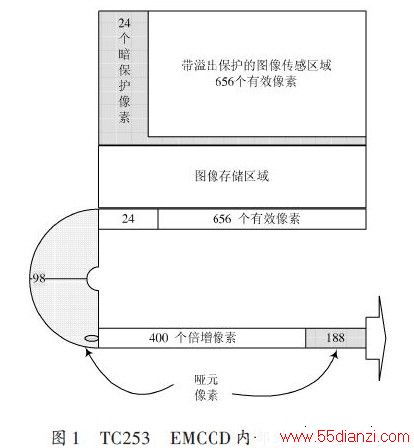

TC253 是一款具有680(H)×500(V)像素的帧转移CCD图像传感器,其结构图如图1所示。它被广泛的应用于要求高灵敏度、低噪声并且小尺寸的特殊用途的成像系统之中。该图像传感器的像素尺寸为7.4 μm×7.4 μm,具有快速单脉冲清除能力,以及逐行扫描、隔行扫描、行合并三种读出模式。在本系统设计中,使用的是逐行扫描模式。

TC253 属于帧转移结构的EMCCD 器件,其面阵分为图像传感区(亦称成像区)和存储区两部分,如图1所示。上电工作时,光学影像照射到图像传感区的像素上,对应像素的势阱会产生并收集电子,形成一幅电子影像。在曝光结束以后,这幅电子影像在成像区和存储区的垂直时钟驱动下快速转移到图像存储区域。此后该电子影像在存储区的垂直转移时钟的驱动下,逐行地转移到水平寄存器中,并在水平转移时钟的驱动下,通过水平串行寄存器转移到输出放大器。TC253 的水平串行寄存器分为前后两部分,前一部分与其他CCD 图像传感器的设计一样;后一部分则是独特的,包含400个级联的电子倍增寄存器,在这些倍增寄存器前后还有一些过渡的哑元像素,具体级数与位置如图1 所示。

这400个级联的倍增寄存器是该器件最具特色的部分,根据所施加的倍增电极电平高低和工作温度,可以进行电子影像的放大。要使EMCCD能够准确无误的读出光电图像,需使光电子能有序地进行垂直与水平的交替转移,并通过放大与相关双取样(CDS)电路进行模拟信号处理,最后经模/数转换器(ADC)输出。因此,必须按照EMCCD 以及CDS 和ADC 的数据手册所述的驱动时序来进行相关时钟的时序设计。EMCCD TC253 一共有4 个时钟驱动信号,4 个垂直转移信号(IAG1,IAG2,SAG1,SAG2),3 个水平转移信号(SRG1,SRG2,CMG),一个曝光溢出控制信号(ODB)。在本系统中,为简化CCD模拟信号处理电路的设计,使用了单片模拟信号处理器AD9845B 作为CCD 输出模拟信号的放大、CDS 和ADC电路。

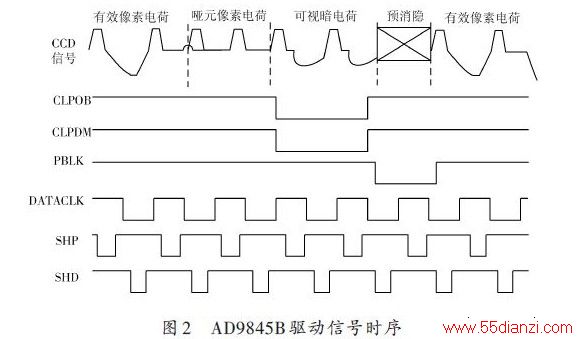

模拟信号处理器AD9845B是一款针对CCD应用的处理器AD9845A 的升级版,亦称为模拟前端处理器(AFE)。它具有30 MHz单通道结构,用于面阵CCD 隔行扫描和逐行扫描信号的调理和采样[8].根据其与CCD对应的时序关系,共需要设置6个时钟驱动信号,分别是相关双采样采集参考电平的时钟SHP、相关双采样采集数据信号电平的时钟SHD、读出数据时钟DATACLK、黑电平箝位时钟CLPOB、输入箝位时钟CLPDM 以及消隐数据时钟PBLK[9].6个驱动信号按照图2所示的时序进行设置,这与AD9845B 数据手册所提供的时序稍有不同。

2 数字系统总体设计思想

由EMCCD 和ADC 的数据手册并结合该项目的要求可知,该数字控制系统就是要实现EMCCD图像传感器在帧转移读出模式和ODB清零模式下的驱动时钟信号,以及在帧转移读出模式下,驱动ADC正常工作的时钟信号。帧转移读出模式有4种水平读出频率,分别为12.5 MHz,6.25 MHz,3.125 MHz,1.562 5 MHz,标准读出频率为12.5 MHz,另外三种读出频率,为了对比测试图像采集的效果而设置的。同时要求可以控制曝光积分时间,选择是否超越读出(OversCAN)。根据VHDL语言的特点,采用顶层模块控制底层模块的方式,即以顶层逻辑控制各个底层逻辑的方式来实现该数字控制系统的功能。这种设计思想在实验室设计的RDCCD 相机[10]、KAISS 相机[11] 中都使用过,控制效果良好,程序结构清晰。

在顶层模块中,定义了一些与底层模块连接的端口,以及数字控制系统与外部硬件连接的端口,设置了顶层模块与各底层模块端口匹配的方式。生成了各个模块需要的各种时钟信号。以及协调了帧转移读出模式与ODB清零模式的切换。

在底层模块中主要是两个子模块:ODB 清零和帧转移读出。每个子模块都有其独立的输入时钟信号与输出端口,在相应模块被选中执行时能顺利完成各自任务,生成正确的输出时钟信号。

3 数字系统的实现与仿真

该设计是在Altera Quartus Ⅱ 8.0的开发环境下,分别对顶层模块和底层模块进行VHDL编程设计与仿真的。下面将介绍各模块的具体设计、仿真过程和一些实现技巧。

3.1 顶层模块的设计

顶层模块中定义了一些输入端口、输出端口和一些与底层模块连接用端口及其映射关系,生成了底层模块需要的各种时钟信号,设置了各模块的切换条件。以clkin作为输入主时钟,生成了3个底层用时钟:清零时钟cLOCk_C,垂直转移时钟clock_V、水平转移时钟clock_H;以clkin_1 μs作为另一输入时钟,生成曝光阶段时钟clock_1 μs.还设置了“cs”,“read_select”,“start_read”三个判断信号,用于选择、切换ODB清零与帧转移读出模式。在Quartus Ⅱ中编译成功后生成顶层模块,命名为top.顶层模块的VHDL 程序流程图如图3所示。

3.2 底层模块的设计

底层模块包含ODB清零子模块与帧转移读出子模块,有时亦称为ODB 清零工作模式与帧转移读出工作模式。下面分别介绍这两个子模块的具体设计过程与仿真结果。

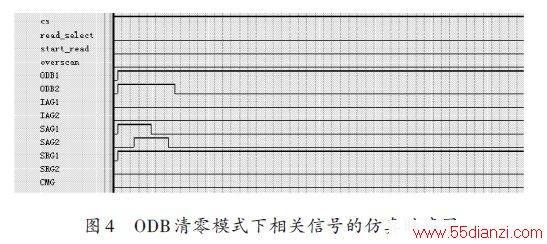

3.2.1 ODB清零模式由顶层模块流程图(即图3)可知,当片选信号cs='1',并且read_select='0‘时,系统将运行ODB 清零模块。该模块就是在系统上电后或CCD未进入曝光工作状态时对CCD 成像区的残余电荷进行清除。根据TC253的数据手册,曝光溢出控制信号ODB在整个图像采集过程中有三个电平值,溢流控制阶段为5.3 V,清零阶段为12.5 V,电荷转移阶段为4.8 V.因此在具体的VHDL编程过程中,可以生成ODB1,ODB2两个信号,将它们输出到一个ODB 驱动电路中,可形成ODB 控制信号。

该模块以顶层生成的时钟信号clock_C作为参考时钟,当清零使能信号start_read='0’时,开始ODB清零过程。在此过程中,垂直转移信号SAG1、SAG2运行一个周期。图4 为该子模块VHDL 程序的仿真结果。通过对比TC253的数据手册可知,仿真波形与该器件要求的时序是一致的。

3.2.2 帧转移读出模式

根据TC253 的数据手册,将该EMCCD 器件的成像与帧转移读出模式划分为4个阶段,按顺序分别是清零阶段S1、曝光阶段S2、垂直转移阶段S3、水平输出阶段S4.在顶层生成的4个时钟信号,分别用作这4阶段的控制时钟,使之能够准确地形成并输出满足TC253所需的各信号。

为了能使4 个阶段的信号顺序执行、互不冲突,在VHDL 程序代码中,需要设置必要的判定信号,以控制状态的转移。这4个阶段的状态转移图如图5所示。由图可知,系统上电后进入初始状态S0,当read_select='1‘时,进入帧转移读出模式。当使能信号C_enable='1’时,进行成像区电荷清除S1,直到结束标志位C_end='1‘后进入曝光阶段S2;当曝光使能位ClrM_en='1’时,开始曝光,直到结束标志位Exp_end='1‘后进入垂直转移阶段S3;当垂直转移使能位V_enable='1’时,开始垂直转移,直到结束标志位V_end='1‘后进入水平输出阶段S4;当水平输出使能位H_enable='1’时,开始水平输出,直到结束标志位H_end='1‘后回到初始状态S0.