分析闪存控制器的架构,首先得了解SSD。一般来说SSD的存储介质分为两种,一种是采用闪存(Flash芯片)作为存储介质,另外一种是采用DRAM作为存储介质。我们通常所说的SSD就是基于闪存的固态硬盘,其采用FLASH芯片作为存储介质。SSD的基本组成结构包括Flash颗粒和Flash控制器,Flash控制器中有芯片,负责Flash的读写、磨损均衡、寿命监控等等。

Flash控制器的主要的工作任务包括三大方面:一是后端访问Flash,管理后端Flash颗粒,包括各种参数控制和数据IO; 二是前端提供访问接口和协议:实现对应的SAS/SATA target协议端或者NVMe协议端, 获取Host发出的IO指令并解码和生成内部私有数据结果等待执行;三是FTL层核心处理。下面我们具体来介绍一下Flash 控制器是怎样做这几件事的。

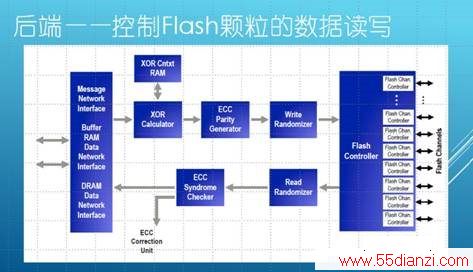

第一,后端访问Flash的操作内容

后端访问Flash首先必须提到的是闪存通道控制器。这个控制器里面有多个通道,每个通道挂多片Flash。它与后端Flash颗粒之间存在托管协议。数据写入Flash的时候,除了主机发送的数据或者原始数据,其他数据都必须进行ECC校验。ECC是通用的称谓,里面有多种算法,其中包括纠错率较低的BCH算法,LAPC低密度校验码等。数据读出的时候,通过扰码,加扰,解扰,看ECC是否出现错误,若有错则在纠错后将芯片发到内部,供后续的程序处理。因此,后端访问Flash的主要任务即是管理后端Flash颗粒,包括各种参数控制和数据IO。

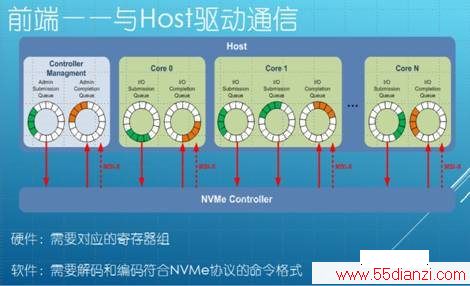

第二,前端提供访问接口和协议

前端提供访问接口和协议,跟主机驱动通信,利用标准格式输配到系统里面,接收主机端发过来的指令,即完成、实现对应的SAS/SATA target协议端或者NVMe协议端,获取Host发出的IO指令并解码和生成内部私有数据结构等待执行。如果遵从NVMe标准,包括提交命令的方法、完成命令的处理方法等都定好了,包括各种队列、队列深度,Queue Pair的总体数量最大可以达到64K个,队列深度也可达64K个,所以,系统里同时可能存在64K×64K IO排着,但是目前的系统是用不到这么多Queue的,因为底下的介质速度还不足以支撑。

第三,FTL层——核心层处理

核心层FTL层,是一款Flash控制器的关键竞争力所在。它既可以是纯软件算法,包括元数据管理,数据布局影射、磨损均衡、垃圾回收、缓存策略、片间RAID和掉电元数据一致性保障等内容。同时,它也可以在进行重复性工作时辅以硬加速引擎。这是非纯软件的,辅有硬加速的成分在里面。硬加速涉及到所使用的芯片。有的芯片支持硬加速,比如说链表的维护。这是因为做垃圾回收时需要要用到链表,拿传统的软件算法,插入一个或者追加一些项目,所耗费的CPU周期较大,此时用硬加速并行,再加上一些硬逻辑的加速,则可节省开销。

Flash控制器的两种策略和方式:

现有的Flash控制器可采用两种方式:一种是少量的强核心加少量硬件加速。所谓强核心就是一个核心的性能高、频率高,分支预判、并行度、单元数量、执行管道,各种参数都高于一般水平。核心强了以后,硬加速就不需要这么多了,可以用少量的硬加速。

另一种方式则是大量弱核心+大量硬加速。比如说16个核心,每个核心比较弱,但是能够增加执行的并行度,有16个并发核心执行,跑16套处理程序,这是两种架构。这是一种多核心协作架构模式,其协作方式可以是同构协作也可以是异构协作

1. 同构协作就是每个核心做的事都是完全一样的,处理的步骤完全一样。如果你的控制器阵列里面有16个IO,有16个核心,每个核心都能处理一个IO,这是同构协作。

2. 异构协作则是多个核心做不同的事情。处理同一个IO,第一个IO第一步,第一个核心处理,这个核心处理完以后,把这个IO扔到下一个核心,再处理下一步,等这个核心空出来以后,处理下一个IO的第一步,这就是所谓的流水线了,所谓的异构就是如此。

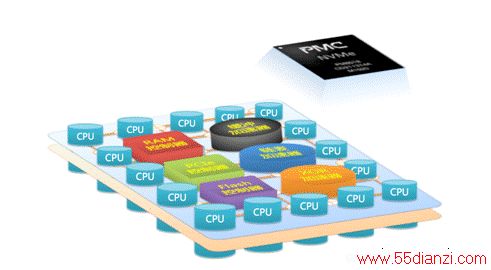

产品实例:PMC的FlashtecTM NVMe 控制器

这是PMC的控制器,首先它有一个片上网络,网络承载16个CPU核心,每个核心里面有一个类似网卡的控制器,网卡连到网络上,多个CPU之间连起来。简单说就是4口路由器或者交换机连起来的网络,多个CPU之间连起来,此外还有硬加速模块。另外还包括以下几部分:

RAM控制器,因为芯片上需要有一定量的RAM放临时数据,写放大,读出来写进去,都要走RAM;

PCIe控制器,这个是跟前端PCIe对等的控制器,IO指令从这儿接收过来;

后端Flash控制器,通过一定数量的通道连Flash颗粒,

加速器(包括缓冲加速器),每做一个操作,都需要有相应的内存,把数据拷到内存里面,内存的维护很费时费力。比如在X86上运行的Linux,其管理内存时需要耗费很多的计算量。对于闪存,精打细算,必须把性能做到极致,因此需用到硬加速。

链表加速器,用链表来记录一些信息,哪块空着,哪块被应用,这块用软件维护很费力,所以需要在这里作加速;

XOR加速器,XOR要用硬加速

最后,来看一下软件的并行度。16个核心,PMC提供的参考的固件,当然SSD厂商会开发自己的固件,把自己优化的东西放进去,优化的算法放进去。基本上包含了这么一些程序,每个IO读的地址可能有重叠,重叠就需要有一个锁定协调,有管命令解析的,有管启动的,有管日志的,有管磨损均衡的,有管查表的,有管写数据的,管前端的PCIe Manager,还有负责boot loader的核心,初始化的配置,需要由它处理,data manager,这是主程序,分析IO指令需要干什么,生成一堆的后续步骤下发下去。其实每一块都可以跑在一个核心上,同一个角色可以复制多份,充分并行。16个核心,达到16份程序并行的运行,16个流水线的Stage,这样就可以屏蔽处理过程中的时延。

本文关键字:控制器 主板-硬盘-存储-插卡,电子知识资料 - 主板-硬盘-存储-插卡