为满足某惯导设备生产厂家对多个惯组产品进行同时测试的需求,设计了一种对于多路脉冲信号同步计数的测试系统。(方法)测试系统以FPGA芯片和USB芯片CY68013为核心,对4个惯导组件输出的48路脉冲信号,每路进行无缝计数,每4ms为一个计数单元。并利用USB总线将每一个计数单元的计数值上传到测控计算机,上位机程序进行实时的处理、保存和显示。(方法)测试系统满足了对多个惯组产品同时测试的要求,提高了测试效率。

惯组产品是现代惯导系统最核心的信息源,由陀螺仪和加速度计组合而成。惯组产品工作时直接输出脉冲信号。测试过程采用专用测试平台,将产品固定在带温箱的三轴转台上,通过在不同的温度下改变转台的位置和速率,由测试系统对其输出的脉冲信号进行计数,再对计数值根据数学模型进行处理,从而得到惯组产品的性能参数。由于温度是影响惯导组件的主要因素之一,所以需要在多个温度点下,对其进行多次测试。而每个温度点需要4个小时的保温。因而完成一个产品的标定,一般需要三天左右的时间才能完成。针对这种情况,本文提出了一种多惯组同时测量的方案,利用FPGA对脉冲信号进行采集,再通过USB总线把采的数据发送到PC机上进行数据归算。与传统的测量系统相比,本系统可以对4个惯导组件的48路脉冲数据进行同步计数并输出,进而有效地缩短测试周期,提高测试效率。

1 测试系统组成

多惯组脉冲测试系统是由下位机和上位机两个部分构成。下位机由FPGA和USB接口电路组成,实现对脉冲信号的计数和数据的接收。上位机是MFC程序设计的界面,对接收到的数据进行实时的处理、显示和保存。由于本系统是同时接收4套惯组48路脉冲信号,所包含的计数器个数多,计数频率高,并且分别对48路信号独立测量,要求较高的可靠性,所以系统采用FPGA来实现控制逻辑及计数模块的功能。系统选用ALTEra公司的Cyclone IIEP2C89208C8N型号的FPGA芯片。在数据传输方面,选用Cypress公司的FX2LP CY68013芯片作为USB传输模块。采集系统框图如图1所示。

在图1中,通过Verilog语言对48路同步计数模块进行设计,实现对48路脉冲信号的同步计数,将接收到的数据通过USB芯片CY68013发送到PC机,由PC机对接收到的数据进行处理,脉冲信号的计数是由无缝计数器,每隔4ms向48路计数模块发送相应的地址,获得48路脉冲计数模块的计数值,再通过USB总线把数据发送到PC机上。

FX2LP CY68013芯片有PORTS、Slave FIFOs和GPIF三种接口方式:PORTS模式以CY68013自带的8051核来进行端口FIFO的读写,其优点是开发简单,缺点是传输速度有限;Slave FIFOs模式是使用外部芯片的逻辑来直接操作端口FIFO,其优点是端口FIFO操作灵活,缺点是传输速度依赖于外部控制逻辑的速度;GPIF模式是使用波形编辑工具生成的波形信号来进行端口FIFO的读写,其优点是传输速度最高,缺点是读写逻辑单一,不容易灵活控制。因为是对48路脉冲信号进行实时采样计数,且每一路脉冲信号采用一个16位计数器,采样周期为4毫秒,即每秒要采集250次。但在实际使用中发现,在PORTS模式下,由于8051内核执行速度有限,在极短的中断时间内有时会不能完成其数据处理和传输的任务,此种状态下USB端就会出现死循环状态。但在Slave FIFO或CPIF模式下,传输和接收的端口将不经过8051内核干涉即可同片外高速互传数据,从而提高接收发送串行信号的效率与可靠性。由于GPIF模式下的编辑波形只能进行读写操作,而在Slave FIFOs的模式下状态机可以对数据进行简单的处理。因此,本系统使用Slave FIFOs的传输模式。

2 系统的FPGA设计

2.1 48路脉冲计数模块设计

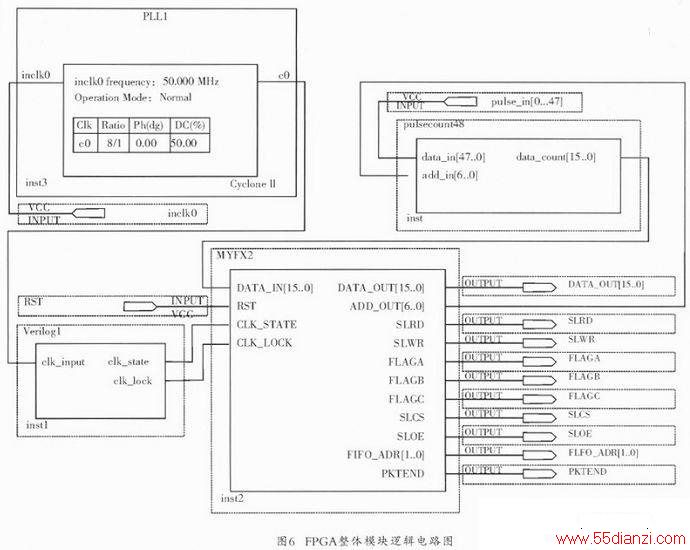

系统的48路脉冲计数模块设计是通过使用Verilog语言编写的16位计数器,可以对惯导组件输出的信号分别进行不间断计数,计数值读取过程不影响计数器的正常计数,该模块data_in[47…0]是48路惯导组件的脉冲输入,add_in [6…0]是每个脉冲输入通道的地址,data_out[15…0]是计数单元的计数值输出。

2.2 时钟分频模块设计

本系统采用50 MHz有源晶振,EP2C8Q208C8N内部拥有两个锁相环,通过倍频使频率达到400MHz,然后连接一个分频模块为状态机提供周期为4ms的计数值锁存信号(clk_LOCk)和一个状态机跳转触发信号(clk_state)。

2.3 状态机模块设计

状态机模块主要包括两个部分:数据处理部分和FIFO控制逻辑部分。

2.3.1 状态机的数据处理部分

状态机在计数值锁存信号(clk_lock)上升沿到来时会锁存计数器此刻的计数值,并在状态机的下一个状态将计数值存储到data-new的寄存器型变量中并进行求差运算,接着将被减数与减数在下一个状态进行更新,最后将求出来的差值交给FIFO控制逻辑进行发送。每个计数单元计数值求差的状态机原理图如图3所示。

2.3.2 状态机的FIFO控制逻辑部分

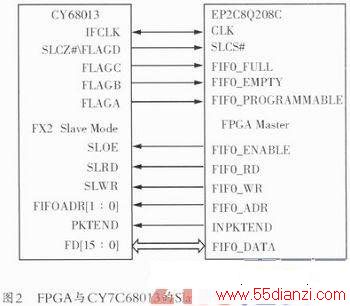

FPGA控制逻辑的主要作用足通过其内部的状态机直接操作CY68013的FIFO来进行读写控制。SLOE、SLRD和SLWR作为芯片的读写信号与使能控制信号。INPKTEND是FPGA主动命令USB芯片向上位PC发送数据的控制端(当FIFO上的数据小于规定大小而又要强制上传给PC时使用)。FD为双向的数据传输接口。FLAGA、FLAGB、FLAGC、FLAGD四个标志位能够指示FIFO的空满程度,为数据的连续存取提供了可靠的保证。FPGA_ADR0和FPGA ADR1用于选择内部4个缓冲端点之一。IFCLK提供时钟信号(仅用于同步Slave FIFOs模式)。FPGA的引脚控制这些端口,达到对USB端的存储FIFO进行操作的目的。由于异步Slave FIFOs模式的读写状态简单,稳定性好。本系统选择异步方式来读取FIFO。

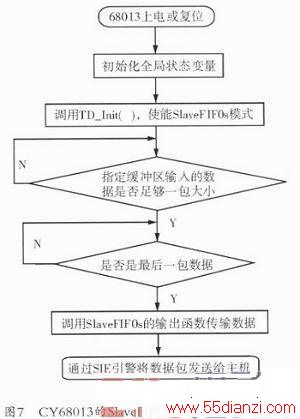

实现异步Slave FIFO的写操作的状态机如图7所示。其状态转移进程如下:

IDLE:此状态为空闲状态,什么也不做;当写事件发牛时(即CLK_LOCK的上升沿到来时),进状态1;

状态1:使FIFOADR[1:0]指向IN FIFO(即就是选择CY68013的四个大数据量FIFO中的一个,固件程序已将此FIFO配置为写模式),进状态2;

状态2:如果FIFO满标志为假(即FLAGC引脚为高电平时),则进状态3;否则在本状态等待;

状态3:驱动数据到数据线上,使SLWR有效(低电平),一个CLK_STATE后再无效(高电平),以使FIFO写指针递增,进状态4;

状态4:如需传输更多的数,返回状态2,否则进状态IDLE。

状态跳转示意图如图4所示:

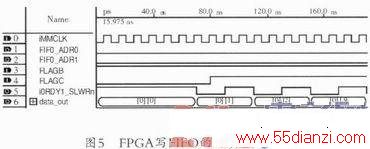

使用QUARTusII对FIFO的控制逻辑进行时序仿真如图5所示。

2.4 FPGA整体模块设计

FPGA整体模块逻辑电路图如图6所示。

3 系统软件设计

3.1 CY68013的固件程序设计

担任着一个系统最基础工作的程序才可称之为固件程序,比如计算机主板上的BIOS。固件程序的作用就是辅助硬件完成预期的设备功能。如下图7所示,同件程序在CY68013上电之后,首先通过调用TD_Init()函数来完成对多个状态寄存器的配置。接着,固件程序会不停检查FIFO中写入的数据大小,当足够一包的数据时自动发送数据包。当发生最后一包的数据不足一包的大小时,INPKTEND引脚在接收到信号后会强制打包上传FIFO中的数据。

3.2 应用程序设计

应用程序的开发采用MFC框架来设计应用程序,实现从USB芯片的FIFO中读取一定大小的数据包并进行实时的处理,以及在用户界面上实时地显示数据。由于文巾的数据包为每4ms的实时数据,数据包读取频率很高,因此.应用程序采用多个函数连续读取多个数据包以后再去启动数据处理和显示的线程,通过实验发现这样可以有效地降低数据处理线程的启动频率,保证MFC应用程序的稳定运行。首先,对所有的函数类进行初始化,并调用Win32函数CreateFile来得到设备句柄,根据设备句柄来连接USB设备。通过接收USB总线的数据包,来获得实时的数据。然后,再对实时的4ms的数据进行处理,求出每秒的脉冲数并进行实时的显示和保存为txt文档。应用程序数据采集流程图如图8所示。

本文关键字:暂无联系方式传感-检测-采集技术,电子知识资料 - 传感-检测-采集技术

上一篇:如何借助探头和软件丰富测试功能