PSK解调器是航天测量船船载遥测终端遥测解调单元的重要组成部分,该解调器中的码同步电路是实现遥测正常解调的基础。目前船载遥测终端PSK解调电路仍然采用数字锁相环技术。这里探讨采用一种新型电路代替数字锁相环,以提高电路对码同步的提取性能。并通过理论分析证明,新的改进方案优化了PSK解码同步电路的性能,提高了精度,扩展了带宽,缩短了时间,增强了可靠性。

航天测量船船载遥测终端PSK解调器由PSK解调和码同步两部分组成。主要功能是从PCM-PSK信号中解调出副载波和PCM信号,并从PCM信号中提取码同步。并对PCM信号积分和最佳判决,恢复出信号的信息,并把各种码型的信息流还原成NRZ—L码。

在数据通信系统中,数据信号是以码元形式逐个地发送和接收的,这就要求发、收双方的时钟要有一个稳定而可靠的同步关系。另外,在接收端无论是经解调得到的基带信号,还是由基带传输所直接得到的基带信号都可能存在一定程度的畸变和干扰,这也要求本地码元定时与发送端定时脉冲的频率相同,且选择最佳的判决时刻以保证对接收信号的最佳取样和判决。通常,把在接收端产生码元定时信号的过程称为位同步或码元同步。码同步是实现正确数字通信的基础,只有取得正确的位同步之后,才能实现字同步、帧同步和副帧同步。如果同步不良,则对码元的判决就不准确,就会使传输误码率大大增加,甚至根本不能正常解调。实现正确码同步的重要性由此可见一斑,这也对PSK解调器中码同步电路提出了较高的要求,因为该电路是遥测正常解调的关键。码同步信号一般直接从数据码中提取,目前大多应用数字锁相技术。为了提高位同步精度,通常用PSK信号的相干载波作为数字锁相环的时钟。目前遥测终端设备中,PSK解调器码同步电路也是采用的数字锁相技术。

1船载遥测终端PSK解调器中码同步锁相环工作现状1.1工作原理

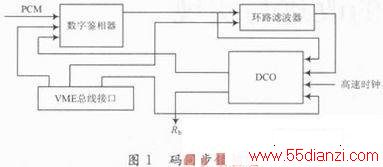

船载遥测终端PSK解调器码同步锁相环如图1所示。

该码同步锁相环采用全数字锁相环。工作原理如下:输入PCM信号与本地信号在数字鉴相器进行相位比较。鉴相器输出相位误差,环路滤波器对输入的噪声及高频分量进行抑制,并且根据环路相位差的大小,控制环路相位校正。

可控置位式数控振荡器DCO根据相位误差的大小对环路分频器进行调整,从而达到改变输出频率相位的目的。

1.2存在缺点

目前采用的船载遥测系统PSK解码同步电路锁相环存在以下缺点:

(1)结构较复杂。数字锁相环路法,一般需要近100个触发器,比较耗费资源。

(2)同步建立时间与精度互为矛盾。锁相环路是一个反馈结构,这种反馈结构使它的同步建立时间和调整精度变成了一对矛盾。由以上的数字锁相环路可以看出,数字鉴相器输出的超前/滞后脉冲,如果输出脉冲步长较小,所需锁定时间较长,且失步后,重新锁定的时间也较长,丢失的数据较多;步长加大可以减少锁定所需时间,但同时锁定精度下降,产生矛盾。通常采用变阶的方法缩短同步建立时间并保持高精度,但同时产生了结构复杂的问题。

(3)带宽较窄。如果出现信号由于传输或器件发生漂移引起频率偏差较大的情况,锁相环码同步法将无能为力。

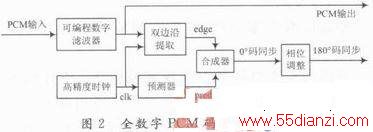

2船载遥测终端PSK解调器采用全数字PCM码同步器针对以上缺点,考虑对码同步电路进行改进,采用一种新型的全数字PCM码同步器,其特点是适应性好,频率跟踪快。整个系统由一个可编程数字滤波器、一个双边沿提取器、一个数字预测器和一个合成器组成。

2.1电路方案设计

电路组成如图2所示。

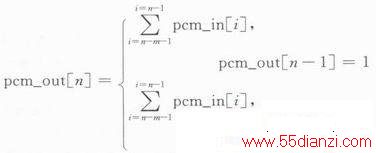

由于输入信号不可避免地存在着各种干扰,这些干扰脉冲将影响码同步脉冲和PCM数据的提取,由此在输入端加一个可编程数字滤波器。该滤波器可根据具体码宽调整滤波宽度,其原理为:设pcm_in为滤波前的输入,pcm_out为滤波后的输出,滤波宽度Ls=To×m,To为高精度时钟clk的周期,输出为:

式中:pcm_in[n]为当前的输入,pcm_out[n]为当前的输出,pcm_out[n-1]为1个时钟前的输出,输入信号经m个时钟滤波后输出。

双边沿提取器的作用是在输入信号的跳变码元的上升沿或下降沿处产生边沿脉冲,是输入信号频率及相位的真实反映,可有效校准码同步器锁定的精度。在同步过程中,当输入的码值发生变化时,将在边沿产生一个跃变,此时双边沿提取器将产生边沿脉冲信号edge,同时控制预测器使其复位,禁止预测输出;当输入的码值为连“1”或连“0”时,无边沿变化,边沿提取器停止工作,无edge输出,此时预测器开始工作,产生预测的本地码同步信号pred,pred由clk分频获得,并由edge对齐相位。边沿提取器与预测器输出的信号经合成器合成输出,二者协同完成码时钟信号的恢复。为了提高数据提取的准确性,解决pred与输入信号频率误差造成的相位移动,将码同步向后移位180°。电路中各点波形如图3所示。

2.2 新同步电路性能分析

假设输入的NRZ—L随机序列的码速率为fin,本地通过预测器产生的预测码速率为fin,输入的NRZ—L随机码序列中的每个码字的宽度为To,随机码序列的最大游程为K(K表示随机序列中连“0”或连“1”的最大个数),可以得到如下结论:

(1)频差的影响。由上述分析可知,当产生频差时,fin≠flo。如果输入的随机序列是由交替变化的“0”和“1”组成,则双边沿提取所产生的边沿脉冲将有效地校正频差;如果输入K个连续的“0”或“1”时,由180°码同步的相位只能偏移±180°,所以只要满足式,就可以保证有正确的码同步信号输出,并能提取到正确的数据。

(2)同步建立时间ts。只要输入的码序列速率与预测器的中心频率之差在上式所示的频差范围内,当出现第一个跳变的码字时,该码同步器就会输出正确的码同步信号。这是因为它是一种开环结构的缘故。

(3)如果信号中断,码同步器输出的是本地时钟经预测器产生的码同步信号f=flo。

(4)同步带宽△fs。由上面的算法可知,它的同步带宽与输入的随机码的游程有关,即:

|△fs|=flo/(2K)

通过与数字锁相环法比较,可以知道:

当输入信号的频率偏差较大时,双边沿提取器可以实时地对预测器输出的码同步信号进行校准,在满足同步带宽的情况下仍可保持同步。在数字锁相环中,需要捕获过程以消除频差。同步建立时间是指在最大相差的情况下,建立同步所需要的时间ts=nTe,Te是一个码元周期,n是分频比。而采用改进电路后,捕获与同步可以在每一个跳变的码元处完成。

3结语

本文提出了一种全新的PCM码同步电路,代替原有的数字锁相环电路,实现码同步功能,以提高电路对PSK载波码元的提取性能。通过以上的对比分析可以看出,PSK解调器采用改进后的码同步电路后,PSK载波码元的提取性能得到了很大程度的提高,精度更好,带宽更大,同步时间更短,可靠性更高,该方案具有很好的推广价值。

本文关键字:暂无联系方式传感-检测-采集技术,电子知识资料 - 传感-检测-采集技术