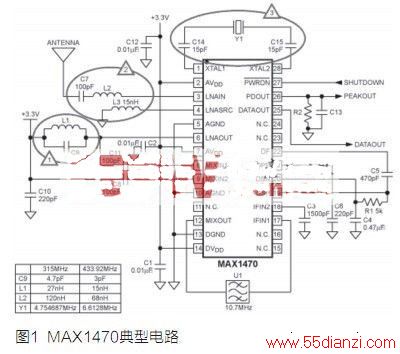

图1所示为基于MAX1470的典型电路,为了改善RF性能,可以对三部分电路进行调整:

● LNA槽路调整 ;

● 输入匹配和电感 ;

● 晶振牵引 。

调整LNA槽路

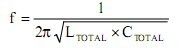

连接在LNAOUT的LC槽路滤波器由L1和C9组成,选择L1 = 27nH,C9 = 4.7pF,使槽路谐振在315MHz RF输入频率。谐振频率由下式确定:

LTOTAL和CTOTAL包括L1、C9以及PCB引线、封装引脚的寄生电感和寄生电容,另外还包括混频器输入阻抗、LNA输出阻抗等,这些寄生参数对槽路滤波器的中心频率影响较大,不可忽略。

为了获得电路的最高灵敏度输出,需要使槽路谐振频率尽可能接近315MHz (或其它目标频率)。因此,用户需要确定电路板的实际谐振频率,然后调整元件参数。最好先去掉晶体,直接由信号发生器产生晶振频率,幅度大约为50mVp-p。RF信号幅度设置为-70dBm,监测RSSI输出(19引脚)。RSSI输出在谐振频率处达到最大,因此很容易找出谐振频率。将RF频率提高640kHz,信号发生器输出频率提高10kHz。更改两个频率后,RSSI幅度会随之变化,偏离最大值。比如,假设谐振频率为345MHz (而不是315MHz),如果引线电感为5nH (与PCB引线长度有关),LTOTAL=32nH,315MHz对应的CTOTAL为7.98pF。由于实际谐振频率为345MHz,实际CTOTAL为6.65pF,为了使振荡频率落在315MHz,CTOTAL必须增大1.3pF,即C9应为6pF。

调整输入匹配和负反馈电感

片外电感的影响可以通过连接在LNASRC (4引脚)和AGND之间的电感L3 = 15nH消除,该电感(除评估板PCB的7nH引线电感外)使LNAIN输入阻抗的实部置为50Ω。C7为隔直流电容,应尽可能选择大电容(100pF甚至更大)。由于LNA输入可以等效为一个50Ω电阻(只要L3 = 15nH,引线电感为7nH)与2.5pF电容串联,LNA的S11可由下式给出:

S11 = 50-j200 (315MHz)或S11 = 50-j145 (433.92MHz)。

选择L2确保与LNA 50Ω输入阻抗(或其它天线阻抗)匹配。因此,为了使MAX1470与50Ω天线匹配,只需要抵消虚部-j。利用L2可以方便地满足这一要求,L2取值为(315MHz时):

L2 = 200/2 × 3.14 × 315e6 = 100nH

借助网络分析仪观察S11可以更好地实现调谐,将网络分析仪的测试口功率设置为-30dBm,以避免输入饱和。图2显示了不是最佳匹配状态下的电路板的S11,S11调谐在355MHz (而不是315MHz)。

如果将电感从100nH更改为355/315×100=120nH,则可得到更好的匹配,如图3所示。

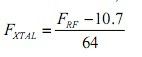

晶体牵引

因为MAX1470使用10.7MHz中频作为低端注入频率,晶体频率由下式确定(单位均为MHz):

对于315MHz应用,晶体频率为4.7547MHz;对于433.92MHz应用,晶体频率为6.6128MHz。

如果电路板提供的负载电容与设计中晶体的负载电容不同,将会导致晶体频率牵引,偏离规定的工作频率,在参考时钟内引入频率误差。这时,需要通过增加外部电容修正负载电容,从而将晶体频率拉回到目标频率。

串联一个牵引电容,将提高晶体频率;反之,并联一个电容将使晶体频率降低。评估板上的等效电容为5pF,使用负载电容为3pF的晶体时,需要串联两个电容(2×15pF)使频率提高。如果不使用这些电容,4.7547MHz晶体的实际振荡频率为4.7544MHz,导致接收器谐振在314.98MHz,而不是315.0MHz,存在20kHz,即60ppm的误差。对于特定的PCB,由于不知道具体的等效电容,可利用频谱分析仪监测IF (确认频谱分析仪通过隔直流电容接入电路),然后通过串联或并联电容的方法,使IF频率“调整”到10.7MHz。

上一篇:MST9U89C处理芯片的特点