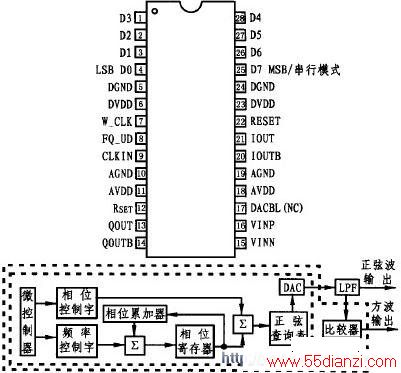

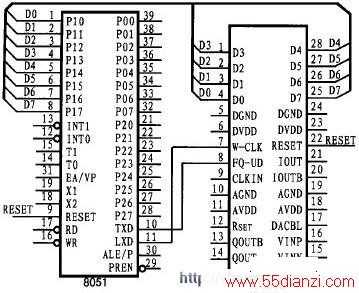

图1 AD9850引脚图

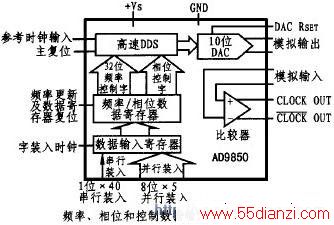

AD9850 内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成。可编程 DDS 系统的核心是相位累加器, 它由一个加法器和一个N位相位寄存器组成, N 一般为24 ~32。每来一个外部参考时钟,相位寄存器便以步长M 递加。相位寄存器的输出与相位控 制字相加后可输入到正弦查询表地址上。正弦查询表包含一个正弦波周期的数字幅度信息 , 每一个地址对应正弦波中0°~360°范围的一个相位点。查询表把输入地址的相位信息 映射成正弦波幅度信号, 然后驱动DAC 以输出模拟量。

相位寄存器每过2N/ M 个外部参考时钟后返回到初始状态一次, 相应地正弦查询表每经过 一个循环也回到初始位置, 从而使整个DDS 系统输出一个正弦波。输出的正弦波周期TO = Tc2N/ M , 频率fout = Mfc/ 2N ,Tc 、fc 分别为外部参考时钟的周期和频率。

AD9850 采用32 位的相位累加器将信号截断成14 位输入到正弦查询表,查询表的输出再被 截断成10 位后输入到DAC , DAC 再输出两个互补的电流。DAC 满量程输出电流通过一个 外接电阻RSET调节, 调节关系为ISET = 32 (1. 248V/ RSET) , RSET的典型值是3. 9kΩ 。将DAC 的输出经低通滤波后接到AD9850 内部的高速比较器上即可直接输出一个抖动很 小的方波。其系统功能如图2所示。

图2 AD9850 的系统功能框图

AD9850 在接上精密时钟源和写入频率相位控制字之后就可产生一个频率和相位都可编程 控制的模拟正弦波输出, 此正弦波可直接用作频率信号源或经内部的高速比较器转换为方 波输出。在125MHz 的时钟下, 32 位的频率控制字可使AD9850 的输出频率分辨率达0. 0291Hz ; 并具有5位相位控制位,而且允许相位按增量180°、90°、45°、22. 5°、11. 25°或这些值的组合进行调整。

2、AD9850 的控制字与控制时序

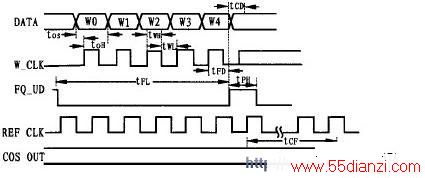

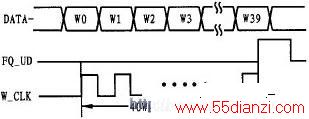

AD9850 有40 位控制字, 32 位用于频率控制,5 位用于相位控制, 1 位用于电源休眠( Power down) 控制, 2 位用于选择工作方式。这40 位控制字可通过并行方式或串行方式 输入到AD9850 ,图3是控制字并行输入的控制时序图, 在并行装入方式中,通过8 位总线D0 ……D7 将可数据输入到寄存器,在重复5 次之后再在FQ – UD 上升沿把40 位数据从输入 寄存器装入到频率/ 相位数据寄存器(更新DDS 输出频率和相位) , 同时把地址指针复位 到第一个输入寄存器。接着在W – CL K 的上升沿装入8位数据,并把指针指向下一个输入 寄存器,连续5 个W – CL K 上升沿后, W – CL K 的边沿就不再起作用,直到复位信号或FQ - UD 上升沿把地址指针复位到第一个寄存器。在串行输入方式, W – CL K 上升沿把25 引脚的一位数据串行移入, 当移动40 位后, 用一个FQ-UD 脉冲即可更新输出频率和相位 。图4 是相应的控制字串行输入的控制时序图。

图3 AD9850控制字并行输入的时序图

图4 AD9850控制字串行输入的时序图

AD9850 的复位(RESET) 信号为高电平有效,且脉冲宽度不小于5 个参考时钟周期。AD9850 的参考时钟频率一般远高于单片机的时钟频率, 因此AD9850 的复位(RESET) 端可与单片 机的复位端直接相连。

值得一提的是: 用于选择工作方式的两个控制位,无论并行还是串行最好都写成00 ,并行 时的10、01 和串行时的10、01、11 都是工厂测试用的保留控制字,不慎使用可能导致难 以预料的后果。

3、单片机与AD9850 的接口

AD9850 有两种与微机并行打印口相连的评估版, 并配有Windows 下运行的软件, 可以作 为应用参考,但运用单片机实现对DDS 的控制与微机实现的控制相比,具有编程控制简便、 接口简单、成本低,容易实现系统的小型化等优点, 因此普遍采用MCS51 单片机作为控制 核心来向AD9850 发送控制字。

单片机与AD9850 的接口既可采用并行方式,也可采用串行方式, 但为了充分发挥芯片的高 速性能, 应在单片机资源允许的情况下尽可能选择并行方式,本文重点介绍其并行方式的 接口。

3. 1 I/ O 方式并行接口

I/ O 方式的并行接口电路比较简单, 但占用单片机资源相对较多, 图5 是I/ O 方式并行 接口的电路图,AD9850 的数据线D0~D7 与P1 口相连, FQ-UD和W-CL K 分别与P3. 0 (10 引脚) 和P3. 1 (11 引脚) 相连, 所有的时序关系均可通过软件控制实现。

图5 AD9850与单片机并行I/ O 方式接口电路图

将DDS 控制字从高至低存放于30H 至34H 中,发送控制字的程序清单如下:

MOV R0 , # 05H

MOV R1 , # 30H

DD : MOV P1 , @R1

SETB P3. 1

CLR P3. 1

INC R1

DJNZ R0 ,DD

SETB P3. 0

CLR P3. 0

END

在程序中, 每将一字节的数据送到P1 口后, 必须将P3. 1 (W-CL K) 置高。在其上升 沿,AD9850 接收与P1 口相连的数据线上的数据, 然后将P3. 1 置低, 并准备下一字节的 发送, 连续发送5 个字节后,须将P3. 0 ( FQ-UD) 再次置高, 以使AD9850 根据刚输入的 控制字更改频率和相位输出, 随后再置P3. 0 为低,准备下一组发送。单片机的P3. 0、 P3. 1引脚为串行口, 当被占用时, W-CL K 和FQ-UD 引脚也可与其它I/ O 脚相连, 这时需要修改相应的发送程序。

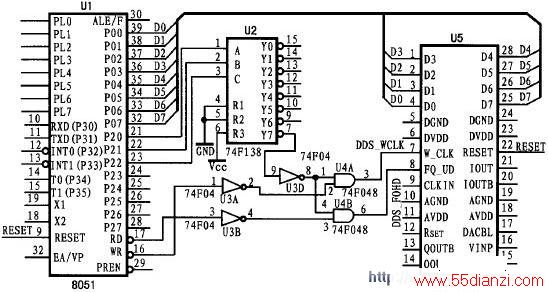

3. 2 总线方式并行接口

总线方式并行接口占用的单片机资源较少, 在这种方式下, AD9850 仅作为一扩展芯片而 占用外部RAM 的一段地址, 必要时也可以只占用一个地址。图6 是总线方式并行接口的电 路原理图。同样将DDS 控制字从高至低存放于30H 至34H 中, 发送控制字的程序清单如下:

图6 AD9850总线方式并行方式接口的电路原理图

MOV R0 , # 05H

MOV R1 , # 30H

MOV DPTR , #0700H

DD : MOV A , @R1

MOVX @DPTR ,A

INC R1

DJNZ R0 ,DD

MOVX A , @DPTR

END

AD9850 的W-CL K 和FQ-UD 信号都是上升沿有效, 用MOVX @DPTR , A 指令向AD9850 传送控制字时, 由74F138 将高八位地址的低三位译码, 其输出经反相并与反相后的信号相 与得到一上升沿送至AD9850 的W-CL K 脚, 此时已送到总线上的数据将被AD9850 接收,连 续五次将40 位的控制字全部发送以后,用MOVX A , @DPTR 指令产生FQ-UD 信号, 使 AD9850 更改输出频率和相位,此时读入到单片机内的数据实际上无任何意义。图6中 AD9850 的地址为0700H。

上述两种接口方式经实际应用证明:工作可靠,效果良好。单片机与AD9850 的串行接口可 参照有关资料进行设计。上述接口电路和程序也适用于与AD9850 脚对脚兼容的AD9851 , 值得注意的是:AD9851 的控制字与AD9850 控制字中个别位的定义稍有区别,编程时应予以 注意。

上一篇:MAX262使用说明