AD9851是AD公司最新推出的采用先进CMOS技术生产的具有高集成度的直接数字合成器,内置32位频率累加器、10bit高速DAC、高速比较器和可软件选通的时钟6倍频电路。外接参考频率源时,AD9851可以产生频谱纯净、频率和相位都可控且稳定度非常高的正弦波,可以直接作为的正弦信号发生器。

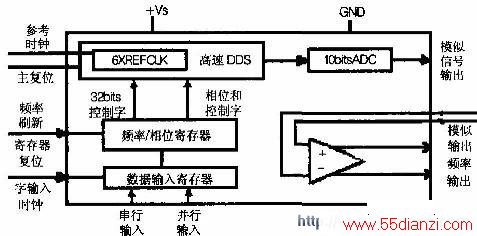

AD9851的内部结构如图1所示。

图1 AD9851内部结构图

AD9851 内部的控制字寄存器首先寄存来自外部的频率、相位控制字,相位累加器接收来自控制字寄存器的数据后决定最终输出信号频率和相位的范围和精度,经过内部D/ A 转换器后,所得到的就是最终的数字合成信号。

AD9851的高速DDS 内核接收外部总线送来的共40位的控制字,前面的8位分别为5位的相位控制字、一位用于电源休眠控制、2位用于选择工作方式,(无论是并行还是串行,最好都写成00,并行时的10、01和串行时的10、01、11都是工厂测试用的保留控制字,不慎使用可能导致难以预料的后果。)剩余32位是频率控制字,在180 MHz系统时钟的情况下频率分辨率是0. 04 Hz,相位最小步进是11. 25°。AD9851的可编程功能主要是通过对内部的5个输入数据寄存器写入40位的控制字来实现的。控制字的写入有并行和串行两种方式,并行方式通过数据总线D0~D7来完成,串行方式把D7上的数据按位串行移入到输入寄存器。两种方式都由W_CLK引脚接入的控制字写时钟来触发写入的。控制字写完后,在FQ_UD信号的上升沿作用下,控制字被写入频率/相位数据寄存器,更新DDS的输出频率和相位。

AD9851的各引脚功能如下,引脚排列,如图2。

图2 AD9851引脚图

D0~D7:8位数据输入口,可给内部寄存器装入40位控制数据。

PGND:6倍参考时钟倍乘器地。

PVCC:6倍参考时钟倍乘器电源。

W-CLK:字装入信号,上升沿有效。

FQ-UD:频率更新控制信号,时钟上升沿确认输入数据有效。

FREFCLOCK:外部参考时钟输入。

CMOS/TTL脉冲序列可直接或间接地加到6倍参考时钟倍乘器上。在直接方式中,输入频率即是系统时钟;在6倍参考时钟倍乘器方式,系统时钟为倍乘器输出。

AGND:模拟地。AVDD:模拟电源(+5V)。

DGND:数字地。DVDD:数字电源(+5V)。

RSET、DAC:外部复位连接端。VOUTN:内部比较器负向输出端。VOUTP:内部比较器正向输出端。

VINN:内部比较器的负向输入端。VINP:内部比较器的正向输入端。DACBP:DAC旁路连接端。

IOUTB:“互补”DAC输出。IOUT:内部DAC输出端。

RESET:复位端。低电平清除DDS累加器和相位延迟器为0Hz和0 相位,同时置数据输入为串行模式以及禁止6倍参考时钟倍乘器工作。

本文关键字:暂无联系方式元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:74LS165简介及应用