图1 AD7713引脚图

1、AD7713的引脚定义

AD7713为大规模集成芯片,其24个引脚(参看图1)分别定义如下:

SCLK (1):串行时钟的输入/输出端,可用MODE脚的状态来控制。当MODE=1时,芯片工作在内部时钟方式,此时SCLK脚输出的是一个串行时钟信号,当 RFS或TFS变低时,SCLK被激活;而当RFS或TFS中的一个为高或器件完成一个输出字的传送后,SCLK转为高阻态。当MODE=0时,芯片工作在外部时钟方式,此时输入的串行时钟可用作数据传送的移位脉冲。

MCLK IN(2):器件的主时钟信号输入脚,其主时钟信号可由石英晶体或外部时钟提供。使用石英晶体时,石英晶体可直接跨接在MCLK IN和MCLK OUT引脚之间;使用外部时钟时,该脚可由与CMOS兼容的电平来驱动而将MCLK OUT脚悬空。输入时钟的频率最高为2MHz。

MCLK OUT(3):当主时钟用石英晶体或陶瓷谐振器时,应将该石英晶体或陶瓷谐振器连接在MCLK IN与MCLK OUT引脚之间。

A0(4):地址输入,当A0为低时,对器件的控制寄存器进行读/写操作;当A0为高时,对器件的数据寄存器或校准寄存器进行读写操作。

SYNC(5):逻辑输入,当系统使用多个AD7713时,使用该引脚可实现各芯片内部数字滤波器的同步。

MODE(6):逻辑输入,当MODE=1时,器件采用内部时钟方式;当MODE=0时,器件采用部时钟方式。

引脚7~10:这四个引脚分别为模拟输入通道1、2的正、负输入端。

STANDBY(11):逻辑输入,当该引脚为低时,将切断器件内部模拟和数字电路的电源,从而使AD7713处于低功耗状态。

AVDD(12):模拟正电源,+5~+10V。

RTD1(13):恒流输出,通常为200μA,可用作电阻式热敏器件的激励电流,该电流可由程序来控制通/断。

REF IN_(14):参考输入,其电位可取AVDD与AGND之间的任意值。

REF IN+(15):参考输入,应注意REF IN+,必须在于REF IN-。

RTD2(16):与RTD1脚功能大体相同,也可与RTD1组合使用,另外,利用此脚可在三线RTD结构中消除引线电阻所产生的误差。

AIN3(17):模拟输入通道3,输入信号幅度可达±4VREF/GAIN,当GAIN=1且VREF=2.5V时,AIN3的输入范围为±10V。

AGND(18):模拟地。

TFS(19):发送帧同步信号,低电平有效。当TFS=0时,芯片允许写入串行数据。在内部时钟方式下,TSF变低将使得串行时钟SCLK有效;在外部时钟方式下,TSF必须在数据字被写入器件的第一个位之前为低。

RFS(20):接收祯同步信号,低RFS=0时,允许对器件进行数据读取的操作。在内部时钟方式下,RFS变低将使串行时钟和数据同时有效;在外部时钟方式下,RFS变低可使SDATA有效。

DRDY(21):逻辑输出,表示数据寄存器的更新速率,DRDY的每一个下降沿都将指明一个新的数据字传输的开始。当一个完整的数据字传输结束后,DRDY将返回到高。

SDATA(22):串行数据。输入时,CPU将把数据字写入到器件的控制寄存器或校准寄存器;输出时,CPU将读取控制寄存器、校准寄存器、数据寄存器内的数据。

在读操作期间,RFS变低之后串行数据有效;而在写操作期,在TFS变低之后,将在SCLK的上升沿加入有效数据。

输出的数据在单极性输入时为自然二进制代码,而在双极性输入时为偏移二进制代码。

DVDD(23):+5V数字电源。DVDD与AVDD的差不得超过0.3V,否则,芯片将不能正常工作。

DGND(24):数字地。

2、AD7713内部控制字的设定

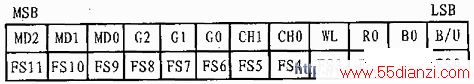

AD7713的工作状态可通过程序向器件内部写入控制字来设定,输入控制字字长为24位。写入时,必须连续写入24位数据,若写入的数据不足,这些数据就不会被加载到控制寄存器中,具体格式为:

图2 AD7713内部控制字格式

格式中的控制字的最高三位用于确定AD7713的工作方式,具体组合如表1所列。G2,G1,G0则用来确定输入通道的增益,可参见表2。CH1和CH0 可确定输入通道号,其编码见表3。当字长选择定义位WL=0时,字长为16位(上电复位时的缺省值);当WL=1时,字长为24位。当激励电流控制位RO =0时,激励电流关断(上电复位时的缺省值);当RO=1时,激励电流接通。熔断电流控制(Burn-out Current)定义位BO=0时,关断AIN端内部的20nA电流源(上电复位时的缺省值);当BO=1时,允许该电流流出,一般情况下,该电流是禁止的。当极性选择定义位B/U=0时,允许双极性输入(上电复位时的缺省值);当B/U=1时,允许单极性输入。

另外,AD7713还在芯片内部集成了一个三阶数字式滤波器((SinX/X)3),该滤波器的截止频率、第一个凹点位置频率及数据率均可由FS11~FS0这12位来编程决定。此外,不同增益下凹点频率还可决定输出噪声电平,以决定器件的分辨率。

图3 AD7713工作方式选择等参数

该数字滤波器的第一个凹点频率为:(fCLK IN/512)/code。

其中code有FS0~FS11位所确定的十进制数,取值范围为19~2000.在2MHz的频率下,凹点频率的范围为1.952Hz~205.59Hz。选择不同的CODE值,可获得不同的凹点频率,从而获得不同的数据转换率。

改变滤波器的凹点频率并选择不同的增益,对分辨率有直接影响。另外,数据转换越慢,其有效分辨率位数越高,因此这种芯片适合于数据采集速率较慢的场合。

3、AD7713的基本连接电路

图1给出了AD7713的基本连接电路。

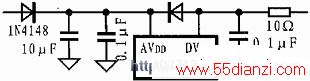

3.1 电源连接

AD7713 的模拟电源和数字电源可分别供电,也可采用单5V电源供电,通常当模拟电源电压大于数字电源电压时,必须分别予以供电。因此这样可减小电源的耦合干扰,提高转换精度,但必须先加数字电源(DVDD),后加模拟电源(AVDD),且要保证AVDD不低于DVDD,因此可在两个电源引脚之间接一个二极管,二极管的负极接AVDD端,正极接DVDD端,以确保DVDD与AVDD的差值不会超过0.3V,具体连接如图2所示。当采用单一电源供电时,应将AVDD端和DVDD端连在一起,或在两脚之间接一个几欧姆的小电阻。

图4 AD7713电源保护电路

3.2 主时钟连接

AD713的主时钟频率最大为2MHz,可以采用石英晶体与内部电路构成振荡器所产生的时钟源频率。频率较低时,也可采用陶瓷谐振器代替石英晶体,但应接入相应的外部电容。主时钟也可直接由外部频率源(TTL或CMOS电平)提供,并由MCLK IN脚输入,此时应将MCLK OUT脚悬空。

3.3 参考电压连接

AD7713设有两个差动式参考电压输入端REF IN+和REF IN-,共中REF IN+端电压(AVDD)应大于REF IN-端电压(>AGND),该参考电压VREF的取值范围为1V~5V,一般限2.5V,其典型的参考源为AD680。

3.4 模拟输入信号连接

AD7713 提供有三个模拟输入通道,其中两个为差动式可编程增益输入通道,可控制为单极性双极性输入,输入的共模电压范围为:AGND-30mV~AVDD+ 30mV。第三个模拟输入通道为可编程增益输入端,可接收的输入信号范围为0~+4VREF/GAIN。若增益取1,VREF取2.5V,最大输入可达 10V。

本文关键字:转换器 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:LM3914N简介及应用