�������ż��ɵ�·�����������켼����eda������Ѹ�ͷ�չ��оƬ���ܶȺ��ӶȲ�����ߣ�������ǰ�����ģ������asicоƬ����һ��оƬ��ʵ��Ƕ��ʽϵͳ�Ĺ����γ���ν��Ƭ�Ͽɱ��ϵͳ�� system on programmable chip��sopc�� �ѳ�Ϊһ�ַ�չ�������ơ� ip core��֪ʶ��Ȩ�ˣ� ��Ƶ��������Լ�sopc �����ij��֣�������Ƶ�����Դ�������˲�Ʒ��������ڣ���������Ƴɱ�����������Ʒ��գ��ӿ��˲�Ʒ�������ٶȡ������н��ܵĴ��пڿ�������һ�ֹ��ܺ�ͨ��Э����MCS-51ϵ����Ƭ���Ĵ��п�����ݣ������д����ߵ�����ͨ�Ų������������ڵ��ٵͳɱ���������λ����ͨѶ�У��������ڴ�����·�Ͻ���ȫ˫����ͨ�š�ͨ��IP�����ü������ɹ㷺Ӧ���ڸ���soc��Ƕ��ʽ����оƬ������Լ���ҵӦ���С�

2 ϵͳ���

�������������altera��˾��max+plus��10.0���ƽ̨���Գ����ټ��ɵ�·Ӳ����������vhdlΪϵͳ��������Ψһ���﷽ʽ�������Զ����µ����ԭ��mcs-51��Ƭ���Ĵ��нӿڽ��з�����ơ�ͬʱѡ��altera��˾��acexϵ��������ʵ�����յ�ip�ˡ�����ƪ���Ĺ�ϵ�����߲�����Կ���ƽ̨�����������Լ�����ʵ��Ӳ����·��fpgaоƬ���н��ܣ��������ؽ�����������˼�롣���ݶ�mcs-51��Ƭ���Ĵ��нӿڿ鹦�ܵ����� [1]��ģ�黯�����˼�룬�����ʱ����ģ�黮�֣��ɻ���Ϊ4����ģ�飬���Ƿֱ��ǣ���1������ʱ�ӷ�����ģ��;��2�����ݼ����ģ��;��3��������ģ��;��4��������ģ�顣����ͬ����·������ʹ�üĴ������첽��λ/��λ�ˣ�����ʹ������·��һ��ȷ���ij�ʼ״̬;ʹ��ͬ����·����������·��ë�̣�ʹ��Ƹ��ɿ�;ͬ����·���Ժܺõ������Ƚ�����ƹ��ߣ��羲̬ʱ��������ߵȣ�Ϊ������ṩ���������������ڵ�·����������ӿ���ƽ��ȡ��������Dz����ϸ��ͬ����Ƶ�·����ƴ��п�ip�ˣ����������ֻ��һ��clk�����أ��Ӷ���֤��ÿһ��������ͬ��������������ʱ�Ӳ�ͬ��������������

3 ϵͳ��ʵ

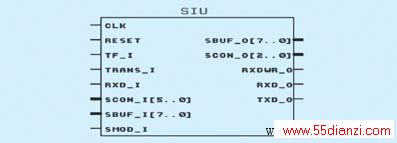

�������һ�����ˣ�����Ҫȷ���������ⲿ����Ϣ����ͨ·������ģ�����ⲿ��·�Ľӿڣ��ѺõĽӿ�ģ�Ϳ��Դ�����ip�˵�ʹ�÷�Χ��ͼ1�Ǵ��п�ip�˵Ľӿ�ģ��ͼ��ͼ����ߵ��������������ţ��ұ���������ţ�ͼ�����ŵĿ��Ⱦ��б�����δд�����ȱ�������Ϊ“1”�������ڱ���Ʋ�֧��i/o�ڵĸ��ã�����Ϊ���пڹ�����ģʽ0��������rxd_o��rxdwr����������ţ�ǰ���������������Ϊ�����Ч����λ��rxdwrΪ�ߵ�ƽʱ��ָʾ����������пڿ��ƼĴ���scon�������Ҳ���ֳ������֣�һ���ֽ������Կ����������루һ��6λ�� sm0��sm1��sm2��ren��tb8��ri����һ������Ϊ���������������һ��3λ��rb8�Լ��ֱ�ָʾ���ͺͽ�����ϵ���λ�����������������λ�����жϱ�־��λ�������ڷ����жϱ�־λti�������䲻��Ӱ�촮�пڵĹ������������ڴ˲�δ�г��������ڿ������еõ����֡�

��������ͨѶ�������ֹ�����ʽ����ʽ0�IJ����ʹ̶��ģ�Ϊ1/12��������ʱ��Ƶ�ʣ�;��ʽ1�ͷ�ʽ3�IJ������Ƕ�ʱ��/������1������ʵ�1/16��1 /32��;����ʽ2�IJ�������������ʱ��Ƶ�ʵ�1/32��1/64�����ɴ˿ɼ������ȱ���Ҫ��������������Ʒ�Ƶ���������ڷ�ʽ0�£����п�������˫����ͬ����λ�Ĵ���ʹ�ã��䷢�ͺͽ��յIJ�������һ���ģ���˶��ڷ�ʽ0�����п��ڲ��ķ�Ƶ�ź�ֻ��Ҫһ·���ɡ����Ƕ���������ʽ�����пھ��ǹ�����ȫ˫����״̬�£���ˣ�ÿ�ַ�ʽ�¾���Ҫ��·��Ƶ�źţ�һ�����ڷ��ͣ�һ�����ڽ��ա�

�������ڷ�ʽ0�ͷ�ʽ2�����Ƶ�Ķ���������ʱ�ӣ�ʵ�����ַ�Ƶ������Ҫvhdl��������£����ź�s_count_enable��Ƶ��Ϊ����ʱ��Ƶ�ʵ�1/12����ߵ�ƽά��ʱ����һ������ʱ�ӵ�������ȡ���

����s_count_enable<=��1��when s_pre_count=conv_unsigned��11��4�� else ��0��;

����p_divide_clk�� process ��clk�� reset��

����begin

����if reset = ��1�� then

����s_pre_count <= conv_unsigned��0��4��;

����else

����if clk��event and clk=��1�� then

����if s_pre_count = conv_unsigned��11��4�� then

����s_pre_count <= conv_unsigned��0��4��;

����else

����s_pre_count <= s_pre_count + conv_unsigned��1,1��;

����end if;

����end if;

����end if;

����end process p_divide_clk;

�������ڷ�ʽ1�ͷ�ʽ3�����Ƶ�Ķ����Ƕ�ʱ��/������1������ʣ��ҷ�Ƶ��ϵ����һ���ġ����ڴ��п�ֻ��һ�����������ܵ��Թ����ڷ�ʽ1��3����˷�ʽ1�ͷ�ʽ3���Թ��÷�Ƶ�źš�Ҫ�Զ�ʱ��/������1������ʽ��з�Ƶ�����ȱ�������Ƶ�ʣ�Ϊ����Ҫһ�������صļ����������ⲿ����Ķ�ʱ��/������ 1������źţ�ͼ1�е�tf_i���ţ��������ļ��������˫��̬��������ʵ�֣�����ƪ����˫��̬��������vhdlʵ����ο�����[2]������Ͳ���������������ڼ�tf_i���ŵ�������ʱ��ʹ������źű���һ��ʱ�����ڵĸߵ�ƽ����������Ƽ������Դ˸ߵ�ƽ���м������Դﵽ�����Ƶ��Ч����

����������Ϊͬ����λ�Ĵ����ķ�ʽ0�⣬������uart��ͨ���첽���պͷ��������õ����ַ�ʽ�ڽ����ⲿ�����ʱ�����Ҫ���ⲿ�������źŲ��������ȷ���źŵ�ֵ�����һ��λ������DZ���ġ�ͬʱ�����пڹ����ڷ�ʽ1����ʽ2�ͷ�ʽ3ʱ��ÿһ�����յ�����֡����һ����ʼλ�������ʼλ���̶�Ϊ0��Ҳ����˵�������rxd_i��1��0������ͻ��������չ��̣�ע���������������ⲿ�������ŵIJ���Ƶ��Ϊ�����ʵ�16���������������������������ؼ���������˼·��һ���ġ�λ����������ԭ���ǰ�һ������λ��ʱ���Ϊ16�ȷ֣����ڲ���������16��״̬����ʾ�����ڼ�������7��8��9״̬ʱ��λ��������ⲿ����˵�ֵ���в���������3ȡ2�ı����������������������λ����������յĵ�һλ����0����ô��˵��������һ֡���ݵ���ʼλ��Ӧ�ñ��������յ�·��λ��

���Ĺؼ��֣���Ƭ�� �ۺ�-��������Ƭ��-�����豸 - �ۺ�-����