�����ּ��������������������Ĵ��������Ѿ�������100 k�����ϡ�Ȼ��������������ߵļ�����ļ���������ԶԶ������������Լ����ٶ���ֹ�������ڿ�ѧ���㡢���ʷ���������Ԥ�⡢����ģ�⡢ͼ�����Լ�ʵʱ�źŴ������Լ���������ٶȵ�Ҫ����Ϊ���С����Ű뵼�弼����Ѹ�ٷ�չ�����ó����ģ���ɵ�·��ƵĴ�����Ԫ����Խ��Խǿ��Ȼ�������������ܵ�����ܵ���������ơ���ˣ�����������ٶȵľ�����Ŀǰֻ��ͨ�����д���������ʵ�֡���

1����

�����������һ�ֲ����źŴ���ϵͳ������Ҫ�ص��ǣ�

��1������ǿ��Ĵ���������������ɶ����źŴ���ģʽ��

��2���źŴ�������ͨ�������źŴ���оƬ��DSP���IJ��м�����ɡ�

��3���źŴ������ܵĸı�ͨ������ʵ�֡�

ͼ1��ʾ���Ƕ�Ŀ�����״��źŴ���������Ҫ��ɲ��֣������еĴ���ģ���DZ���Ҫ����Ĺ�������������

2������㡢CFAR��⡢M/N���

2.1�������

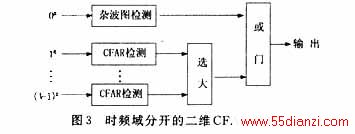

�������ָ�Ӹ����ݼ�������Ⱥ���λ����ʹ��

2.2CFAR����M/N���

�״��źŵļ�������ڸ��ű����Ͻ��еģ�Ϊ����ǿ��������ȡ�źţ�����Ҫ����һ��������ȣ����ұ����к��龯�����豸�����龯������Ŀ���DZ����źż��ʱ���龯�ʺ㶨����������ʹ�������������龯̫������ء�

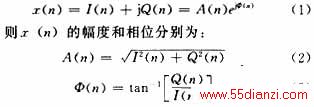

��1����Ԫƽ�����龯��CFAR�������

�Ѿ�֪�����ڵͷֱ��ʵ������״��У����˺���ѩ�ȷֲ��Ӳ����Կ����ܶ�������䵥Ԫ�ز��ĵ��ӣ�����Ӳ�����ķֲ����������ֲ��������ⱳ���д��ڴ����Ӳ������������ͨ�������Ӳ��ľ�ֵ�õ������������Ӳ��ڿռ�ֲ���δ֪�ԣ����Ӳ���ֵֻ�ܴӱ����Ŀ���ڽ���Ԫ����ã�����DZȽϳ��õĵ�Ԫƽ��CFAR�������Ϊ�˼��������������Ӳ���Ե�ڲ��龯�����������⣬һ�������Ľ���·—���Ԫƽ��ѡ���·����ͼ2��ʾ���ڱ���ⵥԪ�����ߣ�Ϊ�˷�ֹĿ�걾��������ֵ��Ӱ����ճ���һ��������Ԫ����������������

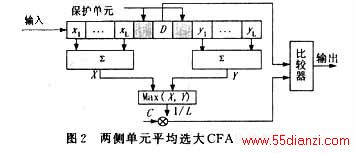

��2����άCFAR�����

���״﹤����FFT��ʽʱ��CFAR��������������ݰ��������Ƶ��2��������������Ҫ������άCFAR����ͼ3��ʾ����0��# �˲���������Ӳ�ͼ�����⣬�����ಷ���˲����������һ����Ԫƽ��CFAR���������CFAR���Ľ����������ΪĿ���жϡ�������������

��3��M/N���

M/N�����CFAR������У����У�NΪ������������MΪС��N��ֵ�������趨M/N������Ϊ2/3������ͬ�����ŵ��ź���3�������ظ�����������2�ι������ж���Ŀ�ꡣ��

2.3�Ӳ�ͼ

�Ӳ�ͼ�������ǽ��״���Χ�Ķ�άƽ��ֳ����λ���뵥Ԫ���ѷ�λ���뵥Ԫ�Ľ����źŴ���һ���洢���У�ÿ���洢��Ԫ��Ӧһ����λ���뵥Ԫ�������������ߵ�ɨ�裬ÿ����Ԫ�洢���źŽ��е��Ƹ��£�

![]()

���У�K��һ��С��1�����ӣ�xn��yn�ֱ�������롢�����

�������߶�Ȧɨ���Ժ��Ӳ�ͼ�д���������Ӧ��λ���뵥Ԫ���Ӳ���ֵ���������H����ʽ

��5�����㣬����������ź�xn��������H�����Ǿ���Ϊ��Ŀ�꣬���������Ŀ�ꡣ

�� H=Cyn(5)

���У�CΪһ�������ӣ�C�Ĵ�С�����ż����ʵ��龯���ʡ���

3ϵͳ�����

���д�����Ŀ����ͨ�����ö��������Ԫͬʱ�������������������ִ��ʱ�䣬���������̵�ʱ����������Ϊ���д��������������ĵ����⣬����һ����ķ�ӳ�����ڴ�������2����������ָ�꣺���ٱȺͲ���Ч�ʡ������д���������2���������ܾ�������ɲ�����������3��Ҫ�أ�������Ԫ�����д���������ṹ�������㷨�����������䷽��������֮�������ϵ��������������

3.1������Ԫ��ѡ��

������Ԫ�����ܿ���˵�Ǿ�����������������������أ������ܵĴ�����Ԫ�������ϵͳ���ܡ�����ϵͳ������ġ����ͽṹ�����Ժ����������ά���ԡ�������Ԫ��Ӧ�÷�Χ���¿ɷ�Ϊ���봦����Ԫ��ר��ASICоƬ��FPGA/EPLD�������źŴ���������ʵʱ�����źŴ���Ӧ���ϣ�DSP�Ծ߱��������ơ�

�ڲ��д����У���ǿ��DSP�Ƿ�������ڹ��ɲ��д�����������ܣ������ͨ�ſ���ͨ�������������������Ľӿڹ��ܵȡ�TMS320C40��ADSP21060�ڽṹ�������кܶ�����֮�������Ƚ϶��ԣ��ۺ����ܽϺõز���DSP��ADSP21060�����������ٶȡ���������������Ƭ�ڴ�����������Զ����TMS320C40���������������DSP������ͻ���ص��ǣ�FFT�ٶȿ졢Ƭ�ڴ����������ܺõع����������ӿڡ����ּ����ͺ�ADSP2106X��ѡ�����Ҳ�ϴ������������Ƴ���ADSP21160������ݣ��ṹ��ӿ���ʽҲ���ơ���

3.2���д����������ṹ

���д����������������Ҫ������Ϊ��������Ԫ�ṩ���ݽ�����ͨ·�������������ͺͿ��Ƶ����źŵĴ��ݡ�������Ԫ֮�������ṹ���¿ɷֳ�2�ࣺ

(1)�������ߣ�������������ϵͳ����Ϊ�����ʽ����ϵͳ��

(2)������Ԫ�и��Զ��������ݴ�������ͨ��ͨ�ſ������ķֲ�ʽ����ϵͳ���ֳ������ʽϵͳ�������ʽ�Ĺ�������ϵͳ�ڴ�����Ԫ�������ٵ�����£�������������ͨ�Ŷ��ܻ�ýϸߵļ��ٱȡ���������Ԫ�����ܶ�ʱ���������߽����Ƶ�������߳�ͻ�͵ȴ������ҹ������߽ṹ�Ŀ������Ժ�����Բ����ֲ�ʽϵͳ�������ڴ��ģ���д���ϵͳ�����ع��������ݴ�������Զ����ֲ�ʽϵͳ��

ͨ�ò���DSP��ͨ�ſ��ٶ���30~60 MHz����Ϊ�ڴ�����Ԫ��Ŀ�ܶ�Ĵ��ģ���д������÷ֲ�ʽϵͳ��ƴ�����������TMS320C40��ADSP21060�ṩ�Ķ��6������ͨ�ſڵ���ͨ����������ָ���ٶȻ�ƽ�����������൱����ͬʱTMS320C40��ADSP21060���ṩ�˹����������ߵĽӿڣ�TMS320C40��2���������ߣ�����һ�������ں�����TMS320C40�������ݣ���ADSP21060��Ƭ�ھ��й��������ٲ��������������������ⲿ���Ƶ�·������£�������

���Ĺؼ��֣�������ϵ��ʽ�ۺ�-��������Ƭ��-�����豸 - �ۺ�-����

��һƪ��ADSP2116x���жϻ�����Ӧ��