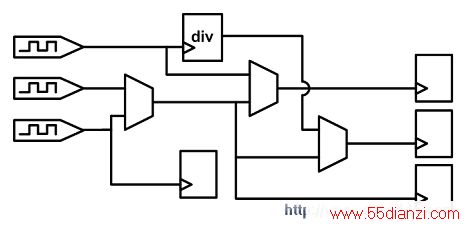

图5网状时钟树结构

IBM常用的 时钟树优化 机制主要由描述时钟树结构的CDOC(CLOCkDesignerOptimizationControlFile)文件和时钟树优化工具BCO两部分组成。基本工作原理为:首先通过CDOC文件确定需要优化的时钟树――CDOC文件描述了各条时钟树的起始点和一个停止点,从起始点开始向后追溯,直到所有分支都遇到停止点为止;其间穿过的结构,就是需要优化的时钟树;然后BCO根据CDOC文件所描述的时钟树结构,按前后顺序依次优化――在优化每一条时钟树段落时,BCO会按照由叶至根的顺序,插入一系列缓冲器或者反向器,使得各个叶节点的时钟到达时间偏差和整个时钟树延迟都尽量小,BCO还会对时钟树穿过的组合逻辑结构进行复制,放在各个叶节点附近,从而满足优化前后逻辑功能的一致性。

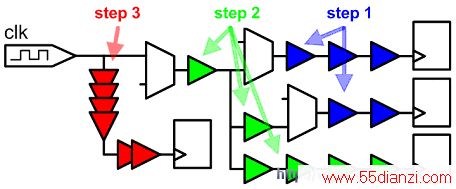

针对通信芯片相对复杂的时钟树结构,BCO在原有机制的基础上提供了一种逐级优化时钟树的方法:如图6所示,首先将整个时钟网络以选通器或分频器为节点分段,按照时钟信号的流向,靠近时钟源的为父时钟树,反之为子时钟树。然后从最末端的子时钟树开始进行优化,并将优化后的延时信息标记在子时钟树的根节点上;优化父时钟树时,根据其所有子时钟树的延迟信息,采用时钟偏差技术(PlannedSkewScheduling),使得其下所有时序器件(包括它的子时钟树)的时钟信号到达时间相同;以此向前递归,直到时钟源;从而实现了整个时钟网络优化。

图6网状时钟树优化方法

2.4HSS

随着信息技术的飞速发展,特别是通信要求的飞速提高,大容量、高速度的业务需求成为了通信系统设计的关键考虑因素。在这种背景下,Serdes(串并/ 并串转换器 )应运而生,并凭借其抗噪性强、传输信道数量少等优点,越来越显示出替代高速并行接口电路的趋势。然而随着数据传输速度和容量的不断提高,信道噪声对信号质量的影响也越来越大,而且不同的业务需求也需要有多种的Serdes进行支持。如何选择一款能够充分满足业务要求的Serdes是大容量通信系统设计中的难点。

针对这种需求,IBM提供了多种型号的HSS(HighSpeedSerdes),能够充分满足客户需求。HSS提供了一种可以在多种条件下运行的 高速串并 转换接口,它保证了发送端数据的低噪声并且能够根据接收数据提取时钟。HSS支持包括从130nm到45nm的半导体工艺,可以达到最高14Gb的数据吞吐率。HSS由接收数据、发送数据和内建PLL三大部分组成,支持双工和单工等多种工作模式。HSS支持多种应用环境,包括电缆连接、扩展连接单元接口(XAUI)、InfiniBand协议、串行ATA接口、串行连接SCSI接口、光纤互联、SONET以及背板(backplane)应用等。

出于减少功耗的考虑,HSS支持多种低功耗模式,所有的数据通道可以被关闭,内建PLL也可以被关闭。通过关闭不需要的通道和PLL,可以节省大部分的动态功耗。另外支持输出端信号强度调节等多种低功耗选择。

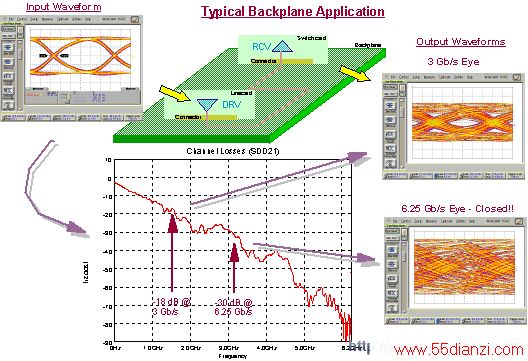

针对越来越复杂的信道环境,为了满足高速大容量业务的需要,IBM为HSS提供了完备而精确的仿真和模拟环境,能够得到精确的HSS配置结果从而得到最佳的信号质量。客户通过提取S-parameter,采用IBM提供的HSSCDR工具或者采用业界通用的AMI模型,以比HspICe高数十倍的仿真速度,得到最佳的HSS配置,调节发送和接受端的内建有限冲激响应滤波器(FIR),配合眼图(Eye-diagram)进行信号质量检测,得到包括频谱分析在内的多种图表,从而有效地辅助客户设计,如下图所示。

图7HSSCDR眼图分析示意图

3小结

本文针对超深亚微米工艺下通信集成电路芯片物理设计的各个难点,提出了相应的解决方案。本文首先分析了由通信集成电路固有特性所决定的,超深亚微米通信芯片物理设计所面临的挑战,如电源网络的稳定、时序的收敛问题、复杂时钟树的优化、高速串并/并串转换器应用等;接着较为详细地介绍了IBM解决方案,如基于ALSIM系列工具的电源网络的分析设计流程、 统计静态时序分析 方法(SSTA)、时钟树优化工具BCO,多种高性能的高速串并转换器及其完备而精确的仿真和建模环境等。因此,IBM所提出的芯片物理设计方法能有效地解决通信集成电路芯片在超深亚微米工艺下的物理实现难点,从而极大地促进通信芯片的开发与应用。

4致谢

在结束之际,由衷感谢IBM 电源噪声 组EdwardP.Sayre博士的在本文写作过程中的悉心指导,感谢IBMHSS专家DanielW.Storaska在HSSCDR方面的大力支持,感谢IBM时序分析专家UweFassnacht在SSTA方面提供的详细资料。

参考文献

[1]ChanduVisweswariah:Within-DieVariationsinTiming:FromDeratingtoCPPRtoStatisticalMethods,Full-daytutorial,InternationalConferenceonComputer-AidedDesign(ICCAD),SanJose,CA,Nov.2007