上文中说到了CycloneIV中的几种配置方式,JTAG或者AS模式配置EPCS64,其中我个人比较倾向于将上文提到的统称为串行配置模式,而EPCS系列的配置芯片都是属于串行配置芯片。而在本文中讲到StratixIII的配置所使用的是FPP模式——快速被动并行模式。配置芯片则不再是EPCS系列了,而是一款CFI Flash。

在此插入一个小知识,ALTEra的Cyclone系列FPGA只支持AS、PS、JTAG这几种串行的配置方式,而更为高端的Stratix系列则另外还能支持并行配置方式了。下面我们详细讲讲它的配置过程。

首先,不管是给EPCS也好,Flash也好,都得先生成适用于它们的SOF文件。

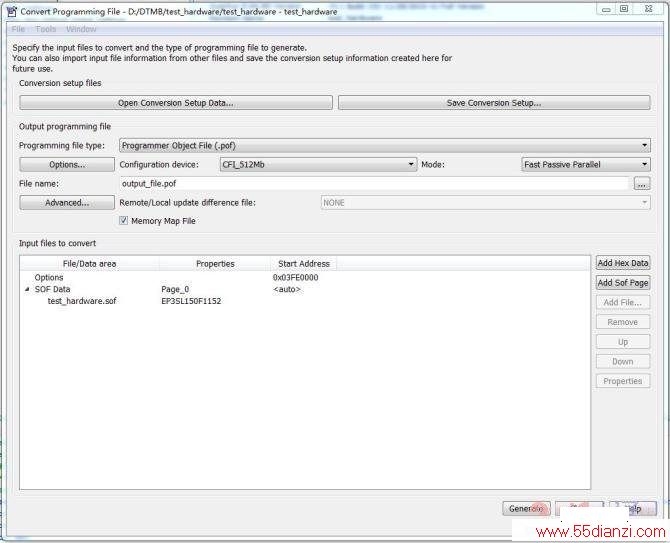

这里和EPCS不同的是,需要设定Flash写入的开始地址,选择option,初始地址设置为0x3FE0000。至于为什么要这样设置,可以查阅相关手册,在后文也会稍微解释这个问题,我们先重点了解配置过程。

有了配置文件,我们是否可以像AS模式配置EPCS那样直接配置Flash呢?答案是否定的。所以这里我们需要借助FPGA,就跟上文中提到的jIC模式一样,通过FPGA来对Flash进行读写。上文中的jic模式,是通过QUARTus提供jic文件,它可以自动将这个过程整合在一起,将FPGA设定为Flash Loader。但在这里,Quartus还没有做到如此完善,需要我们自己手动得将FPGA“设计”成我们的Flash Loader。

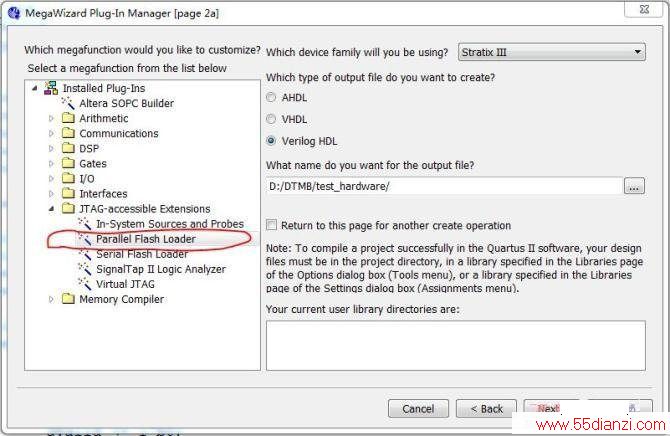

虽然Quartus没能把这个过程设置得像上文中的那么简单,但它给我们提供了一个IP核可用于并行配置:

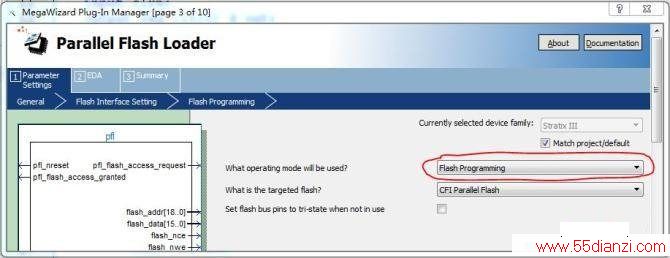

我们可以在新工程中创建这样一个IP核,选择Flash Programming模式:

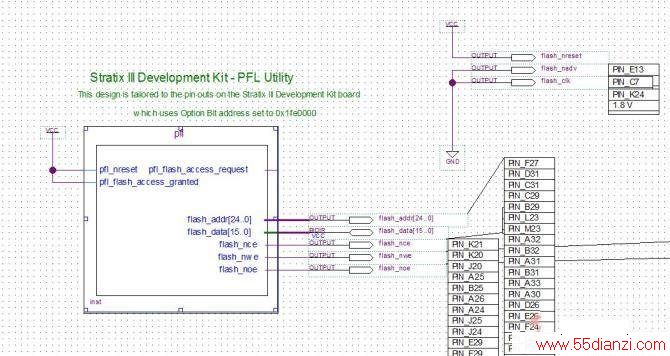

创建好了之后,在顶层原理图中如下图设计:

如此便完成了FPGA Flash Loader的设计,我们将这个工程的SOF文件烧写到FPGA中:

随后回到我们原有工程的Programmer,选择Auto Detect,便可检测到我们的Flash了。

如上图,下方的结构图就和上文中jIC模式时很类似了,FPGA充当了Flash Loader,对CFI Flash进行写入操作。在配置文件选择中,将之前生成的pof文件加入到Flash中,Start后便可完成对Flash的配置了。之后再上电,Flash便会对FPGA进行配置。

在这个过程中可以明显感觉到,这种并行模式的速度要比之前的串行模式快很多,只不过配置过程稍显复杂了。

本文关键字:开发 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术

上一篇:低功耗EDA设计中的巨大挑战