PLL ���������SoC��ϵͳ��оƬ���г�����ģ�� ��· ����������ʱ�����ʸ���30 MHz��SoC������һֻPLL��Ƶ�ʺϳɡ����������ϲ�������һ�֡����ܡ���PLL����������������Ƶ�ʡ����ʡ���������ܺ��ܷ�Χ������100nm���С����ʵ�ֵ�PLL����Ƶ�ʷ�Χ�� 10MHz ��10GHz�����ǵĹ��ʷ�Χ�Ӳ���1mW��ֱ��100mW���ϡ����ǵ�������Դ�0.04mm2��2mm2�������ǵ����ܣ�һ��������������������ӳ���100fs������10ps��

�������Ĺ��Χ����Ϊ���ڶ��������;����Щ��;��������������������ʱ�ӡ�ģ��ǰ��ADC/DAC��ʱ�ӡ�������·ͨ�ţ��Լ�RF�ۺϵȡ����ĵ��ص��DZ�ƵPLL����Ҳ�кܶ��������͵�PLL��

�������ڶ����Լ����ڶ���

����PLL����������ϵIJ����кܶ�ԭ�������ԭ���Ƕ������ܣ���Ȼ����Ҫ�������Ƶ�ʺͻ�·������Ҳ�����á������ԱӦ��Ҫ��ע���ڶ�����period jitter���Լ����ڶ�����long-term jitter�������ڶ����ǵ����ʱ�ӱ�����Ϊ������ʱ������������ʱ���Զ����IJ�������һ��������ڵı��ֽ��ʱ�䣨hold-off�����еġ����仰˵�����������һ��ʱ�������ڵ�������λ����ͨ���������ڶ���ʱҪ�������������ʱ�ӣ������÷��ֵ��rms����������ֵ������

�������ڶ����غ������ֵ�·�ľ�̬ʱ����������磬��1 GHzΪһ�����ֺ����ṩʱ��ʱ����Ҫ1 ns�ı�����ڡ����ǣ�����PLL��ô������Ҳֻ�ܴﵽ1ns��ƽ�����ڡ����ھ�̬ʱ������������˽���С���ڣ����ܼ����ʱ��ԣ�ȡ�����1GHz�����һֻ������PLL�����ڶ�����100fs���������ֶ���ֻռ������ڵ�0.01%���������С�ھ�̬ʱ������еIJ�ȷ���ԡ����һֻPLL�����������С�������ڶ�����1ps?10ps������ֻռ������ڵ�0.1%?1%����ôͨ�����ǿ��Խ��ܵġ�

�������ڶ�������Nѭ�������������ڲ�����N��ѭ���ϣ��ж���PLL�����ʱ����ƫ��������ʱ��λ�ã�����Nͨ������ǧ��ѭ�������仰˵�����ڶ����Dz����ۻ�����λ��һ�㳤�ڶ����IJ������Ϊrmsֵ�������Ƿ��ֵ�����ڶ����Բ���Ƕ��ʱ�ӵĴ�����·ͨ�ŵ�Ӧ�úܹؼ�����ЩӦ�ð���ΪSONET��ͬ�� ���� ���磩��XAUI��10 Gbps���ӵ�Ԫ �ӿ� �����Լ����� ת���� �ṩ��ʱ�ӡ����ڴ�����·ͨ�ţ�������ͨ����涨�����ڶ���ҪС��һ���������ڻ�UI����λ�������1% rms�����磬�����10 Gbps���нӿڹ涨rms���ڶ���ֵС��1 ps��

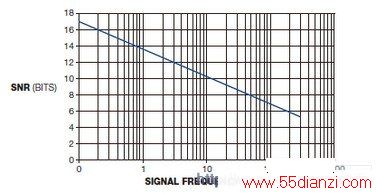

������������ת������ʱ�ӣ����ڶ����ή��SNR������ȣ�����ΪSNR��1/(2���С�F����)������FΪ�ź�Ƶ�ʣ����Dz���Ƶ�ʣ�������rms���ڶ��������Լ�����Ϊһ�ָ�˹�ֲ���ͼ1������һֻADC��SNR��Ƶ�ʹ�ϵ�����ӣ���ʹ��һ����10 ps rms���ڶ�����ʱ�ӡ����ٸ߾���ADC��Ҫ��ȷ��PLL����ʹ10 ps��rms���ڶ���Ҳ������ADC��SNR���Ը���12 MHzʱ������10λ��3 MHzʱ����Ϊ12λ�����Ե���1 MHzʱΪ14λ��

ͼ1 ��һ��������ԴΪADC�ṩʱ�ӣ���ʹSNR������ȣ���

����PLL������

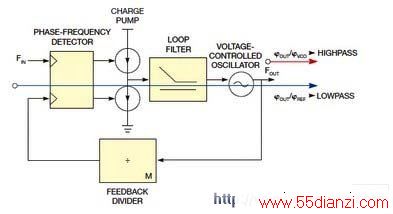

������ɱ�PLL���������漰�ܶ������ԣ��������������ʺ������ͼ2����ʵ��PLL�кܶʽ�������������PLL�������������˽ṹ����������ʹ���Ƶ��FOUT��������Ƶ��FIN���Է�����Ƶֵ��FOUT=FIN��M���ܶ�PLL������һ�����������ij���N���Ӷ��õ���Ƶ��ΪFOUT=FIN��M/N��

ͼ2 ��ɱ�PLL�ж������źŵĵ�ͨ���ܣ�����λ�����ĸ�ͨ����

������ϸ��Ƶ�����������PLLͬʱ���и�ͨ�͵�ͨ�������ο�����1�������뵽���������һ����ͨ��������ζ�ŵ���PLL�����Ļ���λ�����ᴩͨ������ˣ������ڻ�·������������˥���ˡ�����������ʹ�õ�PLL���������������ԣ�ͨ��˥����Ƶ����������ࡱһ����ʱ�ӡ�

����PLL��VCO��ѹ�� ���� ����λ�������и�ͨ���ԡ���ˣ�PLL��˥����Ƶ��VCO��λ�����������ڻ�·��������λ���������͵�����ˡ���������£�����VCO����������ͨ������˥��������PLL����������ϵͳһ�����������Ŵ����������⡣

��������Դ

������һ��������õĵ���PLL�У�������λ����Դ��Դ����VCO����Ȼ�����źܶ���������Դ����ͨ�������ʶȵ�������ʴ��ۣ��Ϳ���ʹ֮С��VCO��������ɱ��뻷· �˲��� һ���ǵڶ�������Դ����·�˲�����������Դ����Դ�ġ�����������ʽ�������PLLһ�㶼����һֻ��ŷķ ���� ����·�ȶ���ͨ�����͵���ֵ�����ӻ��ֵ���ֵ�Լ���ɱõĵ�����ʹ��·��ֵ���ֺ㶨��Ҳ��ʹ��������С�����Ժ��ԡ����ַ����ĸ���ЧӦ�������˹��ʺ������

��������������һ�������ɺ��Ե��������������ǣ����� ��Դ ������������������Ƕ��ڶ�����һ����Ҫ��Դ����Դ����������ͨ����ɱá���·�˲�����VCO�����ڳ��ڶ�������������Ҫȷ������Щ���ֵĵ�Դ�������㹻�����ơ�

�������������

����Ƶ��������������ڻ�·�����Ķ����������ˡ�����ʱ���ʵ����ʾPLL�����Ƕ��ڶ����볤�ڶ���֮������ӡ�ʹ��һ̨ �źŷ����� ��һ̨ ʾ���� �����������Ϳ����������ʱ��ʵ�飨ͼ3�Ͳο�����2������һ��ʵ���������VCO�������ڶ���ʵ�����һ�������˵�һ��ʵ����VCO��PLL�Ķ���������ʵ�鶼��ͨ�������㽻Խ�ı��������������������ô�1��T��N��T��N�α��ֽ��ʱ�䣬����������ʱ��Ĺ�ϵ������TΪ������ڡ�

ͼ3 ʱ������ɲ��VCO�������ϣ���һ������ͬ��VCO��PLL�Ķ������£�

������һ��ʵ�����һ������VCO�ı��ء���N���㽻Խ�ı�����N��ƽ��������һ��ѭ���ı����N=��1��N1/2����һ��ѭ���ı����1�������ڶ�������1��ֵ��ʵ�������Բ�������ΪVCO�� ������ �� ֮����κλ��嶼�ж��������������Ķ��ڶ���Ҳ������һ����Դ����N����ʱ����N��ֵҲ���������������ܻ����rms���������ġ���ˣ��Ӧ�N �CNͼ�п����������1��ֵ��

����һ�����ֵ�ʵ�����Գ����ʾ��ֱ�Ӳ�����1���Ѷȡ�����һ����������ĵ���������30 fs rms����������������rms��ʽ�ۼӣ���ˣ������110 fs rms������VCO�����ӾŸ�����Ϊ30 fs rms�Ļ��壬��ɲ���������200 fs rms����ѭ�����������⣬��Դ������ȫ�ڷ������Ͽ��Ըߴ�100 fs/mV����˺�����ʱ���в���С��200 fs�����ڶ�����

�����ڶ���ʵ���Dz���һ�����������PLL�ı��ء�PLL�������һ������ʵ������ͬ��VCO�����ڼ���ѭ����˵��������������뿪��VCOһ�¡��������ǿ���Ԥ�ڵģ���ΪPLL��Ϊ��ͨ�˲����˵���VCO�����������ܶ��ѭ��������õı����ƽ��˱ջ�������ڶ�����CL��PLL����λ��������������

����ͼ3ǿ���˼�����Ҫ�������ջ�������CL��PLL�ջ�����TL�����ڶ�����1�ĺ��������������ǵ�ɱá���·�˲�����VCO����ij˻��������Է�������ֵ���;�����һ��ϵͳ��ƵIJ������ջ��������ջ��������Ա����ؼ��㵽һ��VCO����T��Ϊ1/(2��FL/FVCO)�����ھͿ��Լ�������ڶ�������CL=��1/(4��FL/FVCO)1/2���ο�����2����

������һ�������ٴ��������ַ�ʽ�ļ����ȣ������ǵ�Ψһ��������VCO��λ������Ȼ����VCO���������˴����������õ�PLL��ע�⣬�˷�����δ���ǵ�Դ��������������ڶ������ǣ��˷����ٶ�PLL��һ��һ��·�������PLL�����Ƕ���·�����ܶ�PLL���й����ᣬ���ڱ�������˵�����ͱ���Ϊһ��·�����⣬���ڶ����Ǵ���ƽ�����ĺ�������˶���һ�����ֹ�������˵������̫���ء�

������Щʵ��ɵõ�������Ҫ�������һ������ǣ����ڵ����ڶ�������ȫȡ����VCO��������壬����PLL�����ء��ڶ�������ǣ����ڶ���ͬʱȡ����VCO��PLL�Ĵ���������Ľ���VCO�������˴��������ڶ���Ҳ�õ����ơ�

����VCO�����

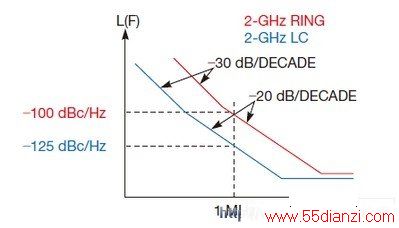

����һ����ͬ���ʵ�2GHz�������������߹��ģ�ͼ4����һ������Ϊ���ͣ���һ��ΪLC�͡�ͼ4�и��������е�������ͬ��������Ҫ����- 20dB /decade�����������ͨ��������VCO�����ڶ�����1��

ͼ4 VCO��λ������������Ȼ��ͬ������

����ͼ�л������VCO��-30dB/decade�����ڸ����ڣ���������˸����һ����ڰ�������������б�¡�������˸������ʹб�����ӣ���-30 dB/decade��-20 dB/decade�Ĺ��ɾ���VCO����˸�սǡ����ڻ���VCO����˸�����սǵĵ��ͷ�Χ��300 kHz��3 MHz������LC��VCO�����Ի�õ���100 kHz�Ĺսǡ�Ӧ��ϸ���Ż�VCO����˸�������⣨�ο�����3����

���Ĺؼ��֣�������ϵ��ʽEDA/PLD��������Ƭ��-�����豸 - EDA/PLD����