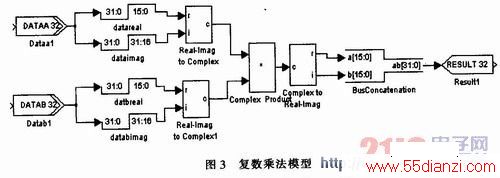

该模型完成了1个16位的复数乘法。在这个设计中,利用Nios32的32位数据位宽,把32位分成2部分,分别放入复数的实部和虚部,实部、虚部的位宽 都是16位,正好构成1个32位数,两个16位复数进行运算后,把结果设为16位复数,也用32位表示。设此模型的文件名为co-mplex.mdl。并 点击Signalcompiler,对complex.mdl进行转换,在转换窗口中分别作如下选择:器件选择CycloneⅡ;综合器选择Quart- usⅡ;“SOPC Info”的generate SOPC Builder PTF File项要选择打勾。分别单击转换按钮1-Convert和综合按钮2-Synthesis即可将其转换成标准的VHDL语言。

2.3 在Nios中加入复数乘法指令

在已建立的SOPC设计中,双击CPU项,点击“Import”按纽,点击“ADD"按纽,打开Complex_ei.vhd,再点击 “Readport-list from files"按纽,点击“ADD to System”按纽,加入该设计作为指令执行模块。最后再将整个项目重新编译一次,锁定引脚后,再下载到目标器件中。为此即在Nios指令中定制了一条名 为COMP的复数乘法指令,在进行C语言编程时,其调用格式为z=nm_comp(x,y),其中x和y为两个复数,其运算结果放在z中。用同样的方法, 可以建立复数加法指令和复数减法指令。由此可见,利用DSP Builder很容易地实现了FFT算法中的复数运算指令的定制。同时在定制指令时,对于浮点数的处理,采用统一为几位二进制有效数字的办法来解决的,比 如说:小数位数固定为4位,整数位数固定为6位,那么可以定义一个向量signal num:std_logIC_vector(9down to 0);在做运算的时候,注意高6位是整数、低4位是小数,就可以达到实型数据的处理。

www.55dianzi.com

2.4 FFT算法软件设计

在NiosⅡ硬件系统设计完成后,将配置文件下载到指定的FPGA中,通过SOPC Builder软件窗口,可进入NiosⅡIDE软件开发环境进行软件设计。

通过SOPC Buider软件窗口,启动NiosⅡIDE,然后新建工程,在新建工程的过程中,选择刚才产生的CPU,新工程产生后,在工程添加文件,在文件中写入程 序代码。在软件编程时设计者可以使用多种方式使用自定制指令,为了简化软件开发者使用自定义指令的编程,在生成的SDK中的.h文件中已经包含了自定义指 令的宏定义,可以直接用在C中。下面以基2,8点FFT为例加以说明。在定制了两条复数运算指令后,可以使用C语言编程实现FFT算法。由于有基本的复数 运算指令和复数加法指令,为此采用C语言编写程序,其算法变得相当简单,FFT核心算法如下:

2.5 系统测试

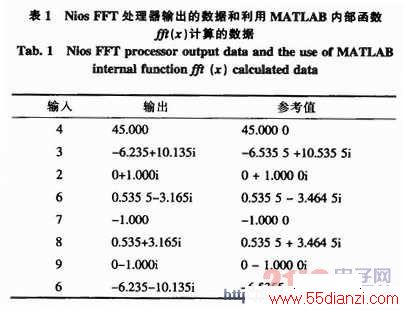

采用ALTEra公司的Cyclone Ⅱ系列芯片EP2C5Q208C8。用Altera提供的Nios SDK,将编译后的可执行代码,通过计算机串口下载到FPGA上的Nios系统内存中去并运行,将输出结果与Matlab仿真结果进行了比较。比较结果如 表l所示,其中参考值是用MATLAB按FFT计算得到的结果,测试值是在Nios中利用C语言编写的FFT程序计算的结果,表中某些数据误差较大,是因 为本系统采用定点数据精度不够,只要增加定点数据的位数就可提高运算的精度。

3 结束语

Nios是一个性价比较高的微处理器,它是以软核的方式提供给用户,并专为在Altera的FPGA上实现作了优化,用于SOPC(片上可编程系统)集 成,最后在FPGA上实现,通过它可以创建Nios CPU设计项目,从而为设计人员提供SOPC设计必需的软硬件设计平台。在定制的NiosCPU设计项目中利用Nios的用户自定义指令功能,可以达到 FFT运算的软硬件协同设计,实现了快速FFT的变换。由于软件直接控制硬件,所以编译过后的软件调试工作,基本上都是软硬件协同完成的。因此速度快,占 用资源少,容易扩展。

本文关键字:协同 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术