数据采集就是通过模数转换器(A/D)将输入的模拟信号转换成数字信号,然后送入单片机中进行处理,而对A/D转换器的启动,数据的读取,数据的传输都是靠MCU(单片机)执行指令来完成的。近年来,随着科学技术的发展,各种型号的模数转换器的性能越来越高,而与密切相连的单片机因其时钟频率较低,很难满足数据采集的实时性和同步性,因此,模数转换器和单片机速度的不匹配,大大影响了数据采集系统的效率,这就要求能有一个读取数据并且暂存数据的接口电路,来作为二者连接的桥梁,为此,基于FPGA的高速数据采集系统的研究显得极为重要。

1 系统整体设计方案

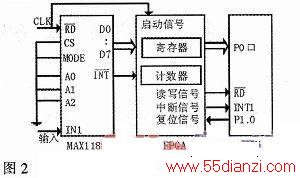

本数据采集系统主要由信号调理通路、数模转换器模块、数据存储与控制模块组成。自行设计的硬件结构框图如图1所示。

信号调理模块是对两路输入信号进行调理的电路。输入信号1是频率为f1的正弦交流信号,先经过整形电路,变为数字时钟信号CLK,送入模数转换器MAX118,作为MAX118的外部时钟输入信号,控制数模转换的速率。另一路输入信号2为采样输入信号,可以是直流信号或是交流信号。当作为交流信号输入时,其频率f2是输入信号1频率f1的1/N倍。N值的大小就是输入信号2在一个周期内采样点的数量。输入信号2经过调理电路处理后,就可以成为满足MAX118输入条件的信号。

将满足MAX118输入条件的信号2送入模数转换器的任一输入通道中,模数转换器将模拟量(输入信号)转换为数字量。

本系统的FPCA设计主要包括双端口寄存器模块和计数器模块,以及一些与MAX118和MCU连接的逻辑控制。FPGA在电路中,一边与MAX118接口,一边与MCU接口,完成数据采集和数据存储的工作。在转换过程中,模数转换器MAX118的启动和读取,复位等控制功能均由FPGA完成。数据采集完毕后,FPGA与单片机之间的数据传输控制指令也是由FPGA发出并完成的。

电源部分由+9 V电源供给,FPGA的电源分别为3.3 V和1.5 V,是用专用电源芯片转换得到,同时还转换得到5 V电源供单片机和MAX118使用,电源的输入电流最大3 A,但不应小于2 A,因为大容量的FPGA在大负荷和资源使用较多时需要的电流较大,此电源的功率可以满足正常使用,不会出现功率不够而使芯片无法正常工作的情况。

2 核心器件工作原理分析

2.1 高速模数转换器MAX118

MAX118是美国Maxim公司推出的低功耗、8位8通道的高速A/D转换器,精度小于1LSB,采样速率达到1.2 MSPs。本方案采用读模式进行采样,可以设计出模数转换器工作在MODE0模式下与FPGA硬件接口电路,通过对引脚的计数,来读取数据。

2.2 现场可编程门阵列(FPGA)及单片机(MCU)

本系统的控制器件由FPGA和单片机两部分组成,在MCU+FPGA组成的电路系统中,单片机主要负责控制,而FPGA主要完成数据的采集和处理,所谓的控制,一方面是单片机直接控制外部电路,另一方面是在FPGA内部自己来写时序电路,满足单片机的读写等时序,从而实现单片机与FPGA联合控制本数据采集系统。

现场可编程门阵列选用ALTEra的Cyclone系列的EP1C6Q240C8,与之相连接的单片机选择使用89C52或者52以上的单片机主芯片,这主要是为了高速的串口通信考虑。

3 FPGA逻辑设计

3.1 FPGA接口电路

FPGA在整个硬件电路中负责在MAX118和MCU之间的缓冲与控制。对于A/D来说,FPGA的主要作用是控制模数转换器MAX118的启动和转换,并暂存采样的数据,通过其内部设计的计数器,完成采样信号一个周期内采样数量的控制。对于单片机来说,当FPGA完成信号一个周期的采样后,向单片机申请中断,由单片机完成对数据的读取以及对FPGA内部计数器的复位等工作。

自行设计的硬件连接图如图2所示。

下面根据图2来具体说明采样过程。

1)MAX118工作过程 要把输入信号送入模数转换器MAX118,必须通过设置其A0,A1,A2 3个引脚来选择输入信号的通道,当A0,A1,A2 3个引脚都为低时,选中通道1,此时,输入信号被送入A/D中。并将外部时钟信号CLK同时送入MAX118及FPGA中,保证二者同时被启动。MAX118的MODE引脚被置低,工作在读模式,至此,A/D可以进行转换,8位数据从D0~D7引脚读出。

2)FPGA控制过程 假设外部时钟信号CLK的频率f1是输入信号频率f2的32倍,输入信号在一个周期内将被采样32个点。当FPGA检测到时钟信号CLK的上升沿时,开始从MAX118的数据输出端口D0~D7读数据,并将数据放入FPGA的寄存器中。同时,FPGA的计数单元开始对MAX118的![]() 计数,根据对MAX118时序的分析,每进行一次转换,

计数,根据对MAX118时序的分析,每进行一次转换,![]() 都被拉低一次,那么当采样完一个周期的32个点后,

都被拉低一次,那么当采样完一个周期的32个点后,![]() 也被计数了32次。此时,由FPGA给单片机一个中断信号,单片机通过FPGA内部设置的地址译码器开始对其存储器中的数据进行读取,而FPGA则处于等待状态。当读取结束后,单片机通过P1.0引脚给FPGA一个复位信号,将其内部计数器清零,然后再开始读取下一个周期的数据,如此循环,周而复始。

也被计数了32次。此时,由FPGA给单片机一个中断信号,单片机通过FPGA内部设置的地址译码器开始对其存储器中的数据进行读取,而FPGA则处于等待状态。当读取结束后,单片机通过P1.0引脚给FPGA一个复位信号,将其内部计数器清零,然后再开始读取下一个周期的数据,如此循环,周而复始。

3.2 FPGA逻辑设计 本设计采用Verilog—HDL硬件描述语言进行逻辑代码设计,在QUARTusⅡ开发环境下,根据需求编写源代码,来完成分析综合,适配,仿真等工作,最后将生成的pof文件下载到FPGA中。

4 系统调试结果分析

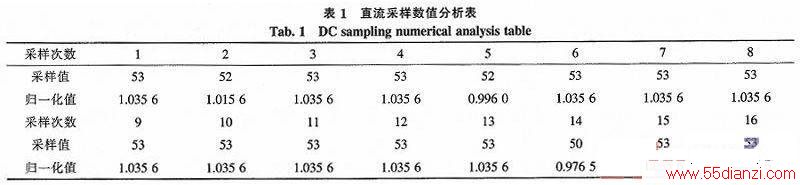

4.1 直流信号采集效果 首先,输入一个直流信号进行采集,来分析采集系统的正确度。

设输入信号1频率f1=160 kHz,经过整形电路变为一个方波信号,作为模数转换器的时钟信号。输入信号2为一个直流信号,设其表达式为u=1 V,然后对输入信号2进行16个点的采样,采样数据如下表所示:

上表中的采样值是经过8位的模数转换器MAX118量化编码后输出的,需要经过归一化处理后,才能用正确度公式![]() 来分析,其中

来分析,其中![]() 表示测量的均值,x表示真实值。通过计算&epSILon;=0.03。MAX118是一个8位的模数转换器,其基准电压为5 V,所以此模数转换器的分辨率为5/28=0.02,也就是A/D引起的量化误差为0.02。

表示测量的均值,x表示真实值。通过计算&epSILon;=0.03。MAX118是一个8位的模数转换器,其基准电压为5 V,所以此模数转换器的分辨率为5/28=0.02,也就是A/D引起的量化误差为0.02。

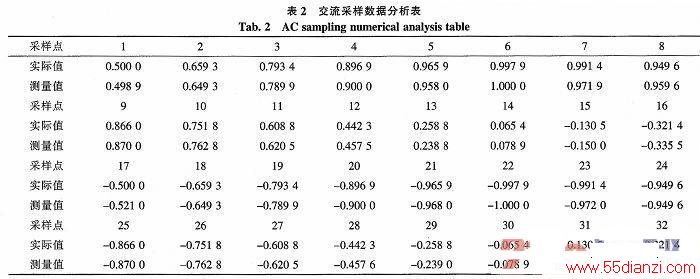

由此可见,系统误差中,除了量化误差外,还存在着别的误差,这是由于电路中的噪声干扰等因素引起的,是不可避免的。这个数据也表明,本设计的准确度很高。 4.2 交流信号采集效果 现在,输入一个交流信号来分析采集系统的精密度。精密度反映在相同条件下,对某定值做多次测量,测量值分散的程度,通过测量值的标准偏差来衡量标准差越小,表示数据越集中。

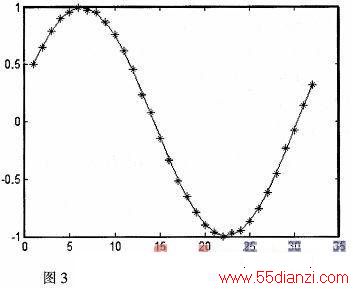

图3是由采样系统输出的测量值画出的波形图,采样数据已经作了归一化处理。

观察上图,发现只有少数采样点偏离实际值,二者的波形形状基本吻合,说明数据采集是成功的。 如表2所示,为输入正弦信号在一个周期内的32个点实际值和采样值数据。其中,采样测量值已经进行了归一化的处理。

本文关键字:数据采集 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术