基于FPGA的高性能加密卡的设计

点击数:7106 次 录入时间:03-04 12:00:35 整理:http://www.55dianzi.com DSP/FPGA技术

模幂运算是RSA加解密的核心,可以通过模乘运算来实现,本次采用蒙哥马利算法实现模乘运算,该算法利用移位和加法代替了复杂的乘、模操作,易于在硬件上实现。NiosII软核中定制的RSA加解密运算指令的输入为密钥、数据长度和启动信号,输出为运算完成信号。当NiosII软核接收到RSA运算命令后,通过定制的模幂运算指令向RSA运算模块写入密钥和数据长度信号,然后启动该运算模块,RSA运算模块接收到Nios II软核的启动信号后,从数据缓存读取待运算数据进行加解密运算,运算完成后将运算结果存入数据缓存中,并向NiosII软核发送完成信号,NiosII软核接收到RSA运算完成信号后启动PCI—E总线接口,将运算结果发送给主机。这样采用软硬件结合的方式实现RSA加解密功能,不但能够保证RSA运算的正确性,降低RSA算法实现的复杂度,而且比采用纯软件实现方式提高了运算速度。

1.2.4 SM1接口电路设计

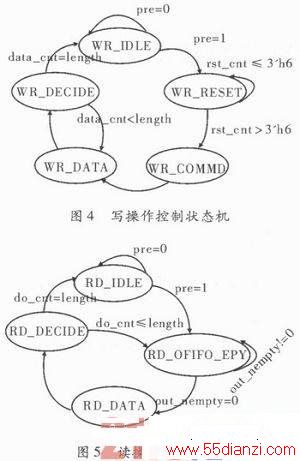

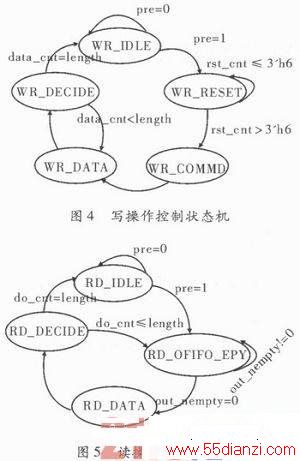

在FPGA内设计有一个专用SM1算法芯片的接口控制电路,用于控制SM1算法芯片实现数据的加解密操作。SM1算法芯片采用双总线命令和组包操作方式,具有较高的运算速率。所以接口电路主要由写状态机和读状态机组成,分别控制对SM1算法芯片进行写数据操作和读运算结果操作。接口电路的工作原理:加密卡上电后,首先对SM1算法芯片进行硬件复位,然后检查由NiosII软核发送的SM1算法启动信号,若该信号有效,则同时启动写状态机和读状态机,这样能够在进行写数据操作时,也读取运算结果值,从而提高SM1算法命令的执行速率。图4和图5分别为写操作状态机和读操作状态机的设计。

2 设计实现

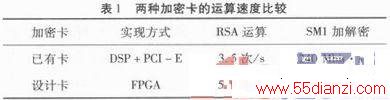

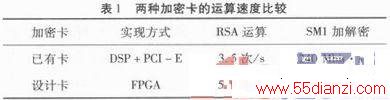

设计采用NiosII Eclipse开发软件完成加密卡软件程序设计,采用QuaxtusII 11.0工具软件完成加密卡硬件电路设计,并对所设计的软硬件进行了整合和仿真验证。在验证设计的正确性后,完成了对FPGA内部整体电路的布局及综合,并制作成加密卡样品。在Windows系统下对所设计的加密卡连续测试168 h,加密卡工作正确;和已有的基于DSP和PCI—E桥接芯片设计的加密卡进行测试比较,结果如表1所示,本次设计的加密卡能够正确地完成各项功能,同时RSA算法的运算速度为5.9次/s,SM1运算速度为295 Mbit·s-1,较已有加密卡RSA运算的3.5次/s和SM1运算的240 Mbit·s-1有了大幅提高,所以本次加密卡在保证可靠性的同时,运算速度更快。

3 结束语

基于增强信息安全的思想,设计了一种基于FPGA的低成本、高性能的加密卡。采用FPGA内部资源实现了加密卡的控制器模块、算法模块、通信接口模块和各种接口等主要功能。并对两种不同结构设计方式的加密卡进行了性能比较测试,结果表明采用FPGA单芯片结构设计方式的加密卡功能正确,电路板结构简单,可靠性强并且具有更高的灵活性和运算速度,达到了预期的目标。目前所设计的加密卡只集成了SM1和RSA算法,今后根据需要,可在FPGA内部通过扩展硬件或软件的方式来增加其它的加密算法功能,所以,该加密卡实用性强,具有可扩展性,在信息安全领域具有良好的发展前景。

上一页 [1] [2]

本文关键字:加密 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术