4 AD时序仿真

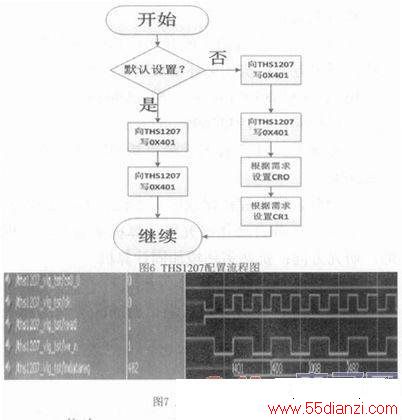

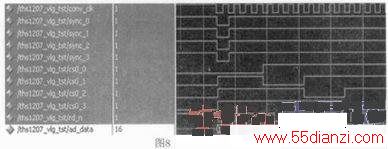

仿真在FPGA的开发中扮演了重要的角色,利用modelsim仿真软件来对编好的AD程序进行时序验证。AD正式工作前,需要通过向AD内部控制寄存器、CR1写命令启动AD,然后才能读取数据。启动AD芯片THS1207的流程图如图6所示,启动AD的仿真结果如图7所示。

AD芯片THS1207正常启动后就可以开始读取各个通道的数据,由于本设计是十六个通道依次采样,采样结束后,需要通过片选控制信号依次读取各个通道的数据,仿真结果如图8所示。

从仿真结果验证得到编写的AD程序可以完成十六道采样的设计要求。

5 实验结果

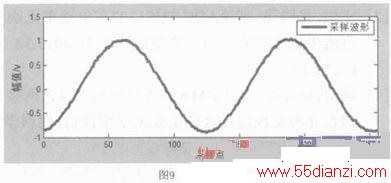

实验采用AD四通道同步采样,利用信号发生器产生正弦波,选择同步采样方式对每个正弦波采样128点,通过以太网传送到上位机,采样得到的波形如图9所示。

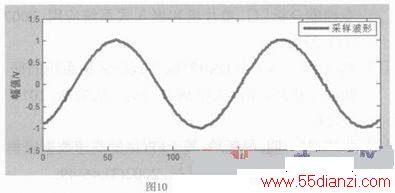

可以利用FPGA的自定义指令,根据需求将得到的数据进行处理,如图10,对得到的波形数据进行偏置为-10和放大倍数为1.05的修正。

实验中当信号发生器发出正弦波的频率达到3000Hz时,即采样频率达到384kHz时,FPGA采集波形能力达到了最大值,相当于180000r /min的旋转机械的基频信号。当超过3000Hz时,采样得到的波形会出现毛刺现象。分析原因,主要是由于nios ii进、出中断服务程序,以及中断服务程序中对采样数据的读取需要花费一定的时间。

6 结束语

本设计利用FPGA并行技术、自定义模块化设计以及nios ii的特色功能即自定制指令,实现了对于旋转机械振动信号的多通道高速同步采样。显示了FPGA可编程、设计灵活、高速的特点,同时也验证了基于FPGA的多通道高速采样系统的可行性。

根据实验结果和理论的最大采样速度还有差距,可以进一步改进系统设计,例如采用DMA优化程序,提高速率。

本文关键字:通道 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术