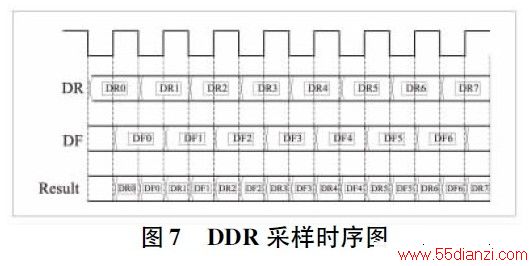

图6 框图实现的时序如图7 所示,从图7 可以看出两路数据在DDR 变换后交替输出,速率提高一倍,其中DR( 数据1) 先输出,DF( 数据2) 后输出。

2 仿真及优化

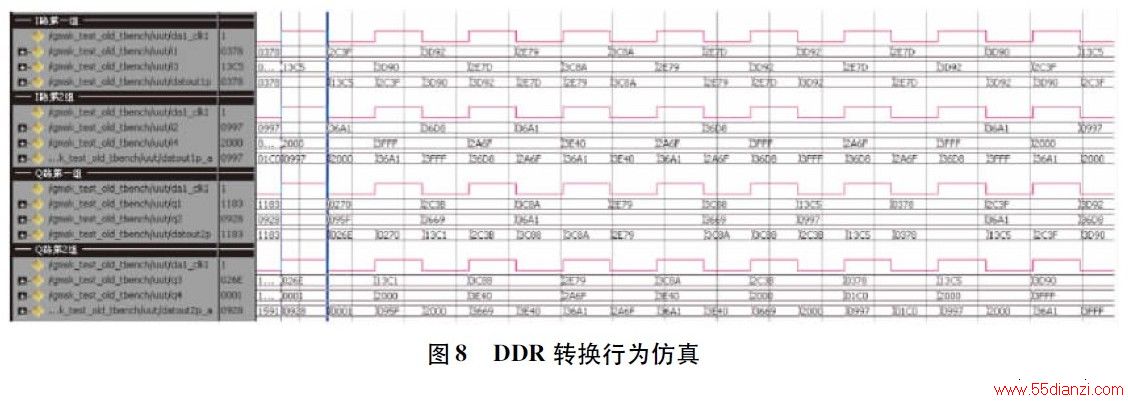

在Actel 公司的编程环境IDE V9. 0 中进行编程仿真。使用Modelsim 6. 5d 进行行为仿真,仿真波形如图8 所示。由图8 可见变换后数据符合预期,功能实现正确。

使用Modelsim 6. 5d 进行布局布线后仿真,仿真波形如图9 所示。由图9 可见各路数据均存在毛刺,毛刺的最大宽度达到了1. 8ns,这超出了DAC 器件对于输入并行数据相位差小于1ns 的要求。可能导致DAC 采样错误。

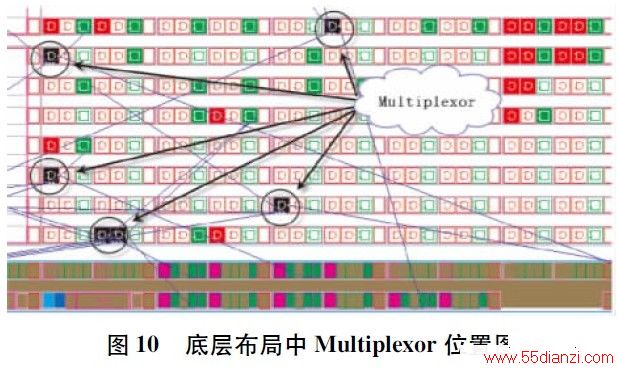

分析最终输出数据毛刺产生的原因,应当是每路数据的14bit 单独信号之间路径的延时不同导致的。而数据在输出之前大部分环节都是由全局时钟进行同步处理,可以保证严格的同步,除了选择器Multiplexor 输出到IO 端口部分走线,因为在Multiplexor的输出环节不会再有时钟采样,因此该部分多路信号延迟差异无法消除。检查布局布线后底层的布局图,如图10 所示,深黑色的单元即为Multiplexor,显然各个Multiplexor 与对应IO 口的距离差别较大,验证了之前的分析。

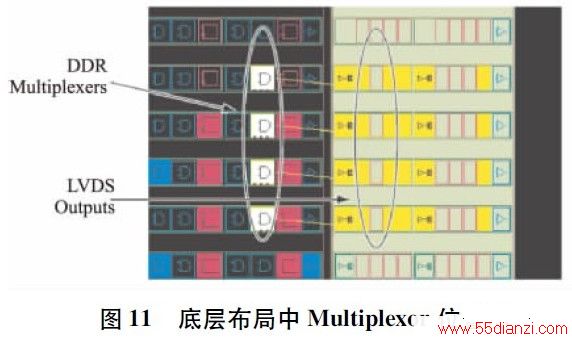

根据前段分析,对Multiplexor 的位置进行手动优化,即在底层布局图中将所有Multiplexor 均调整到尽量接近IO 端口的位置,保证多路信号在Multiplexor后端延迟尽量一致,优化后锁定这些Multiplexor的位置,如图11 所示。

优化Multiplexor 布局后重新进行后仿真,仿真结果如图12 所示。由图12 可见,最大毛刺宽度仅为500ps 左右,完全满足DAC 要求的1ns.可见,优化后的方案合理、可行的实现了要求的功能。

图12 优化底层布局中Multiplexor 位置后的后仿真

文章中阐述的方法不仅仅局限于FPGA 与DAC之间的接口设计,也适用于FPGA 与其他高速芯片的通信,例如FPGA、DSP、SDRAM 等等支持DDR 接口的器件,同时,对于板级及单元级的通信,使用该方法可以有效降低线缆传输信号速率,使得系统各个环节的设计更为简单。

3 结束语

文章分析了Actel 公司反熔丝FPGA 相对于常用的SRAM 型FPGA 在卫星产品中应用的优点,并就一种常见的应用目标,提出基于Actel 公司RTAX-S 系列抗辐射反熔丝FPGA 的高速DDR 输出接口的设计方法,并通过优化得到符合要求的结果,为反熔丝FPGA 在卫星产品中的高速设计、应用提供了技术保障。

本文关键字:接口 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:ARM与神经网络处理器的通信方案