图3 Chipscope系统测试结果

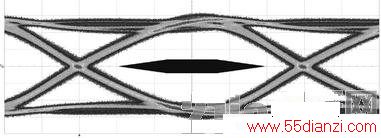

第二部分是运用高频率范围示波器抓取FPGA输出给PHY芯片的数据,以检测该系统传输的信号质量,由示波器测试的数据传输眼图如图4所示。由于4路2.5G的传输链路配置相同且篇幅有限,只是列举出第0路传输数据的眼图。该系统传输的眼图的比特错误率(EyeBER)可达到10-45,眼高为600 mV左右。

图4 高速数据传输眼图

结语

通过反复验证和长时间连续测试,测试结果证明,该设计能够有效、正确地实现10 Gb/s的高速数据传输,并且传输数据的误码均未超过阈值,进而证明了该设计系统的可靠性和稳定性。采用FPGA中的RocketIO接口来设计10 Gb/s速率的光纤传输,极大地增强了光纤传输设计的灵活性,通过修改FPGA代码即可用于高速信号传输的多种情况和场合。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术