测试结果

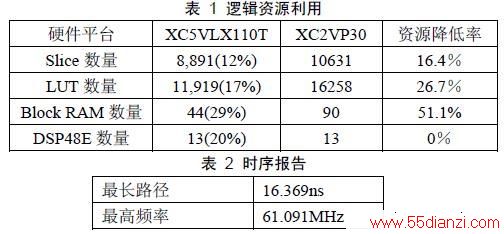

该 系 统 在 Xilinx ML509 开发板上进行测试, 该开发板上采用了一块 XC5VLX110T-FF1136 的FPGA 芯片,测试方案为:将摄像头实时采集到的图像送进系统视 频输入模块,然后经过拨码开关来控制板上的AD9880 芯片转化为384x288 的8 位灰度图送 入核心检测模块检测并输出在VGA 显示器上。整个系统逻辑资源占用情况如表 1 所示。表 2 为最后系统能够运行的最高频率。

结论

本文创新点在于采用了一种像素积分单元阵列结构,能够对 Adaboost 算法中的Haar 特征进行并行处理。结合Virtex5 平台丰富和特殊结构的逻辑资源,得到了理想的性能,甚 至已经能够和高性能的PC 平台相提并论。从结果中可以看到,本系统只使用了部分资源。 通过在FPGA 芯片内部例化更多的处理单元,还有进一步增大并行性以取得性能提升的空 间。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术